Gallery of Chip Photographs

Here are some of the recent chips we designed, fabricated and

tested. Details can be found in our (upcoming) publications.

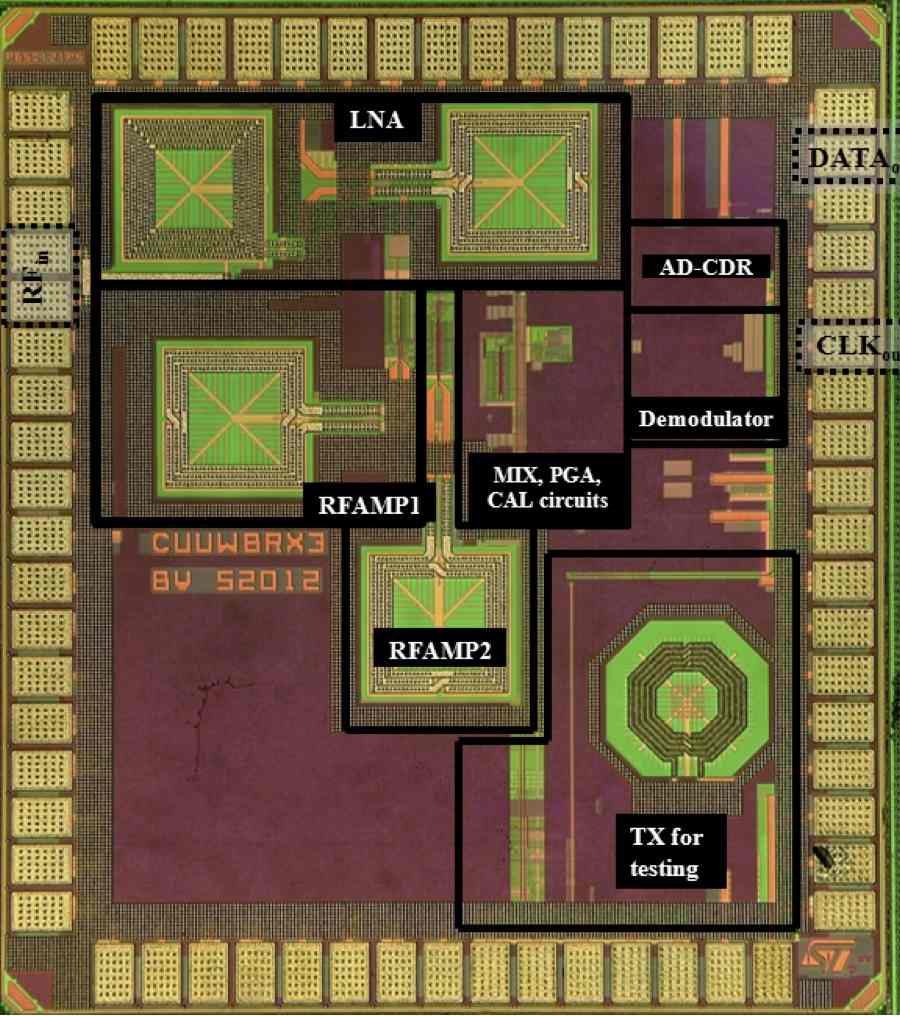

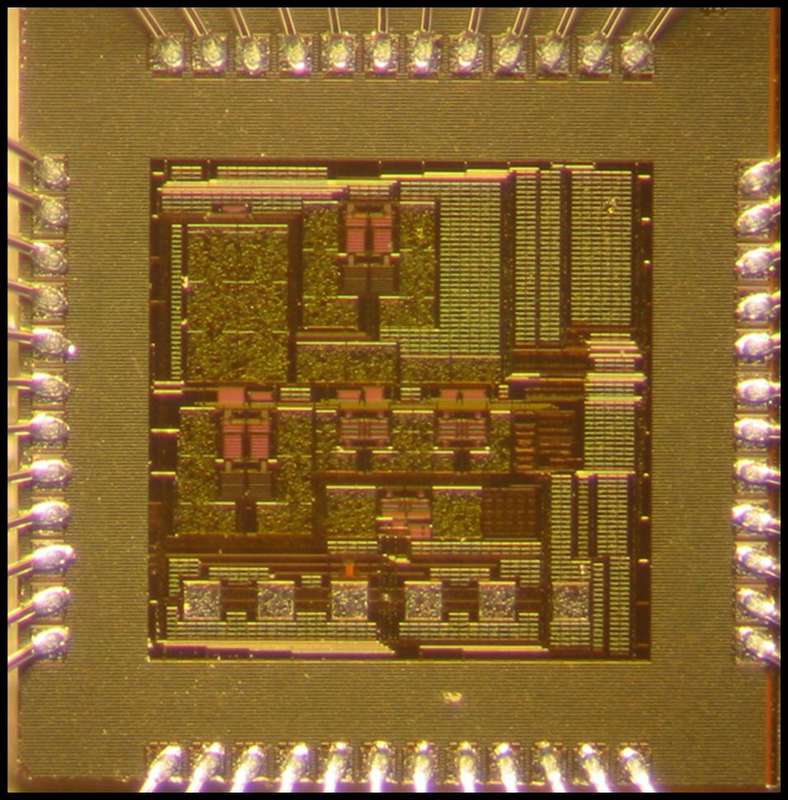

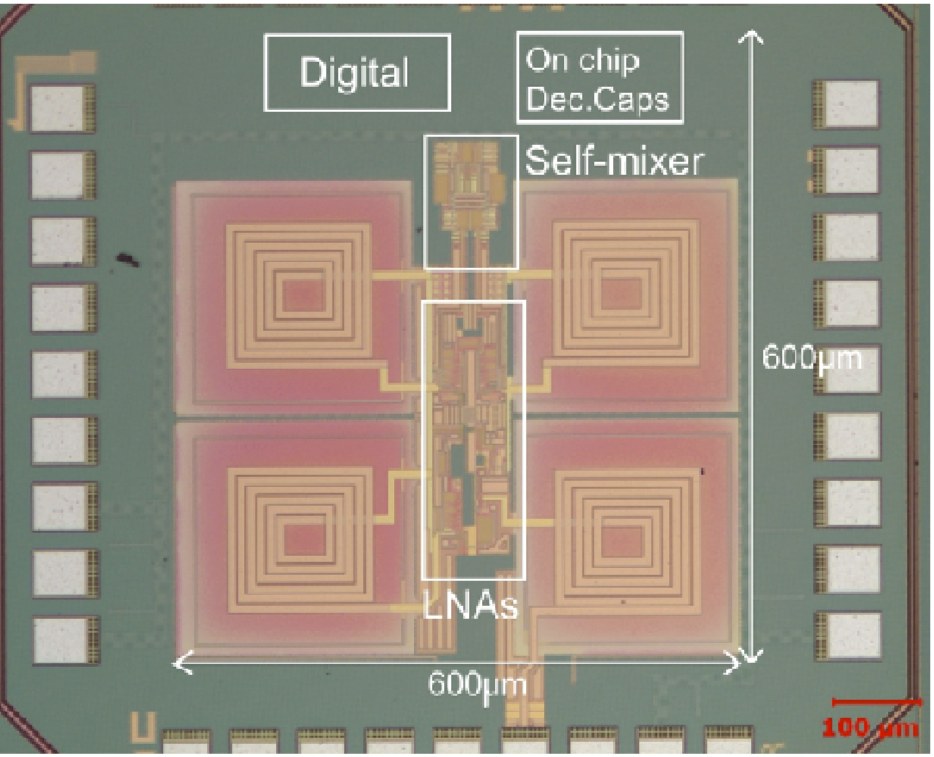

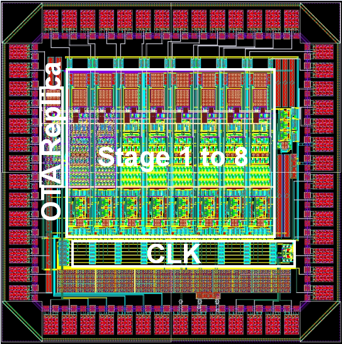

Self-duty cycled, self-synchronized UWB Receiver SoC (65nm CMOS)

[ISSCC13]

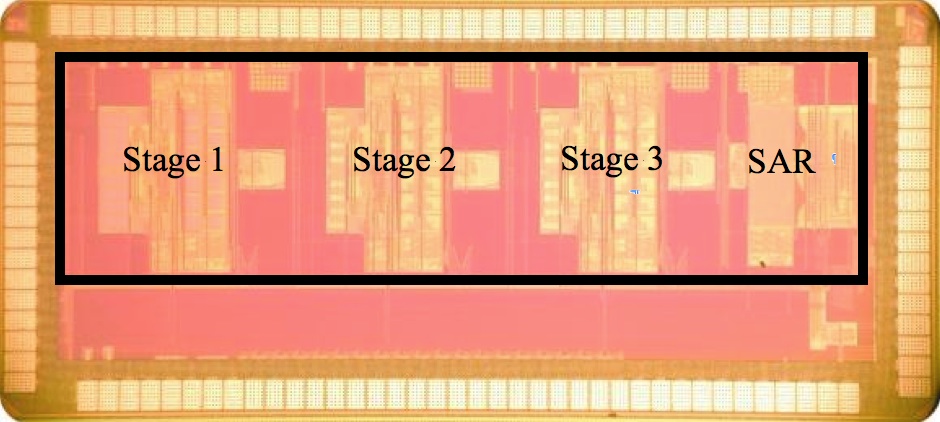

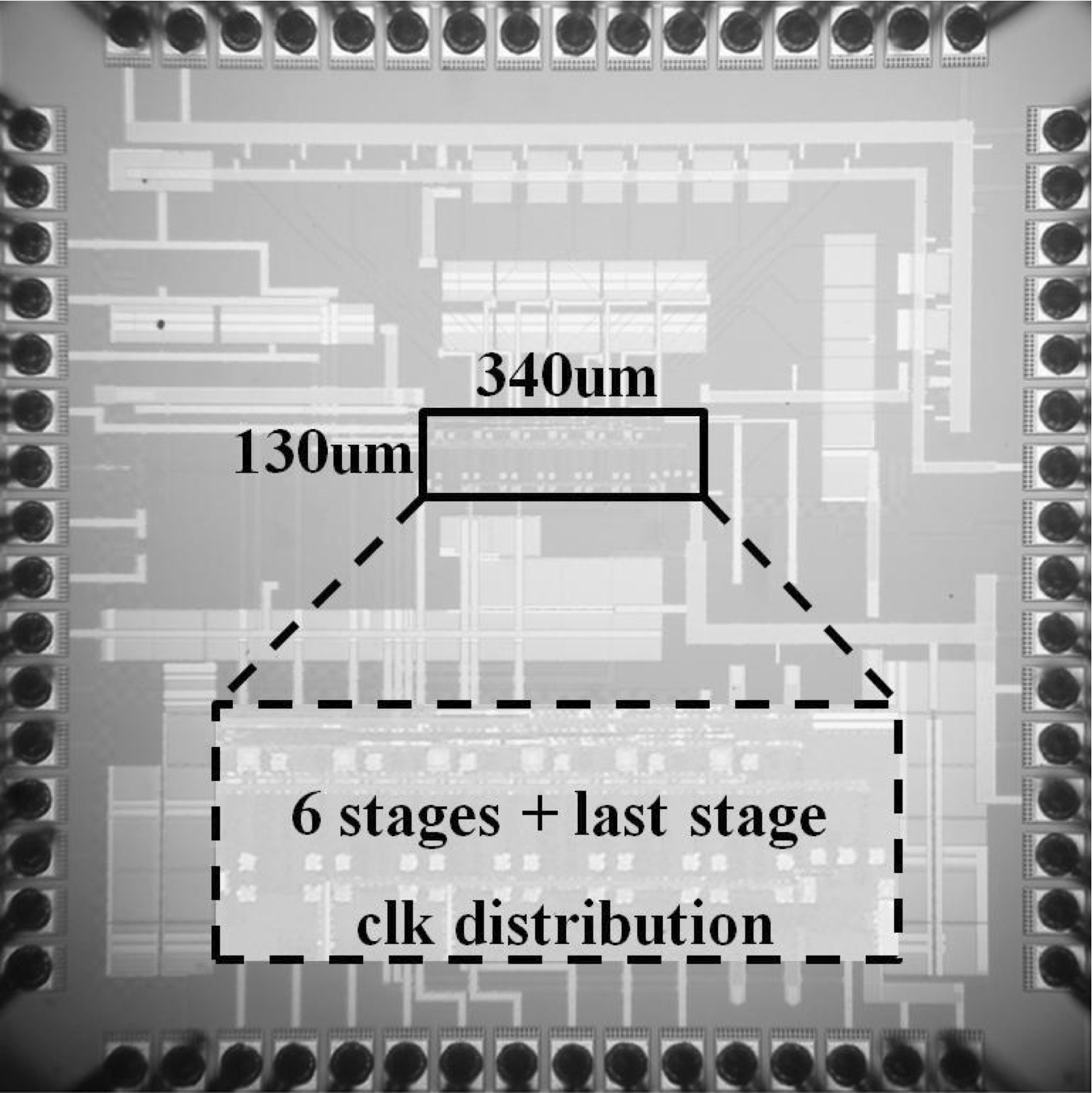

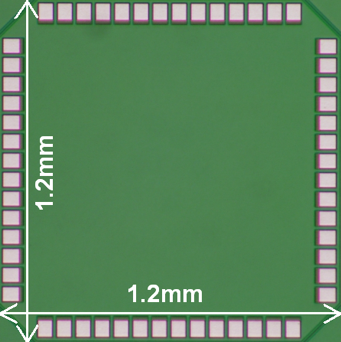

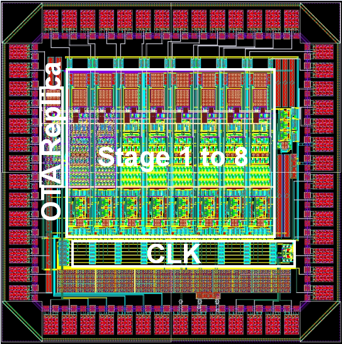

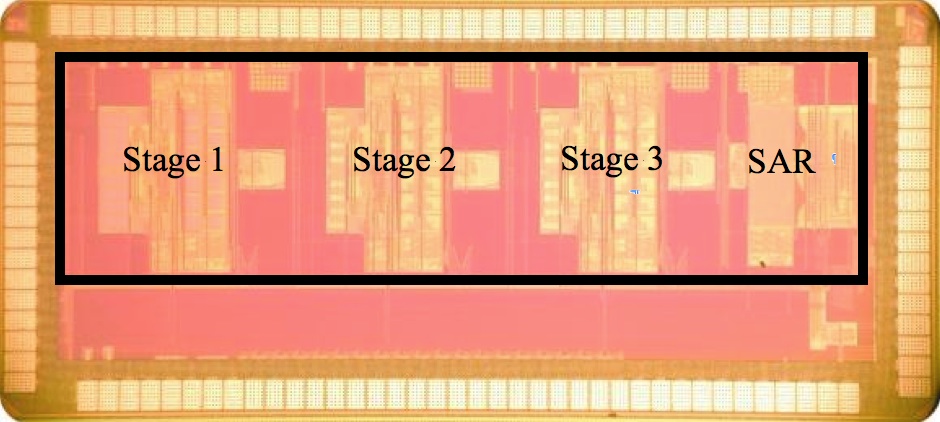

Current Reference Pre-charged Zero-crossing

Pipeline-SAR ADC (65nm CMOS)

[CICC12]

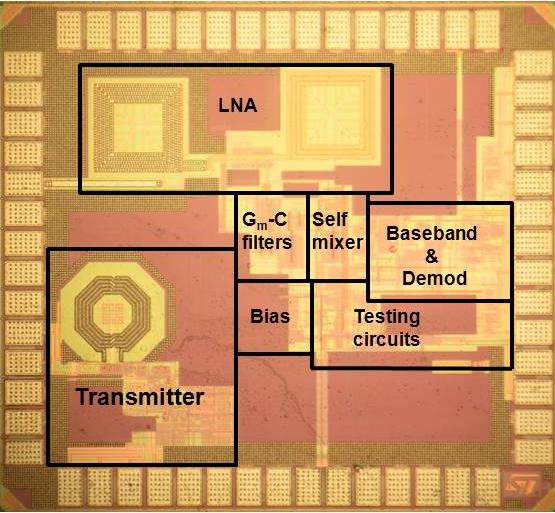

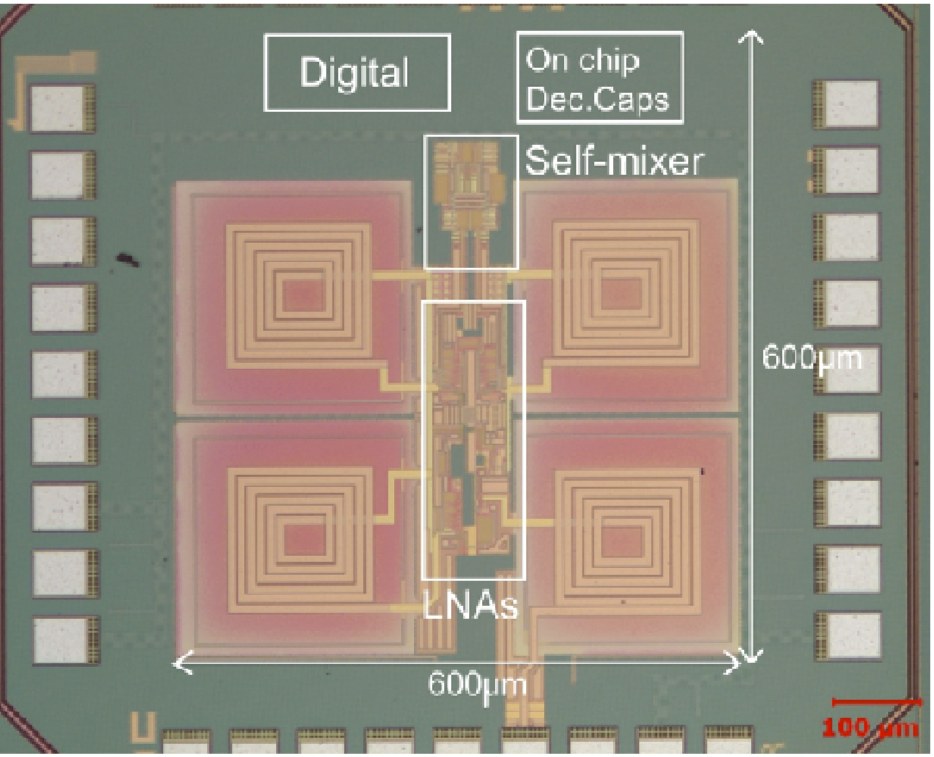

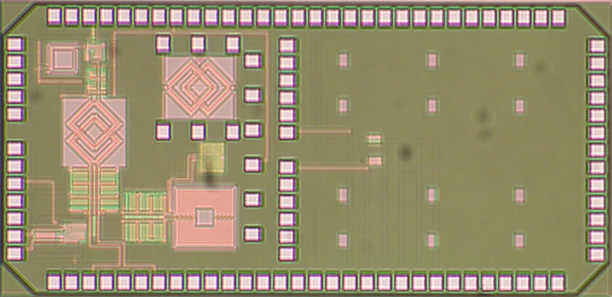

UWB Receiver with Automatic Threshold Recovery (65nm CMOS)

[RFIC12]

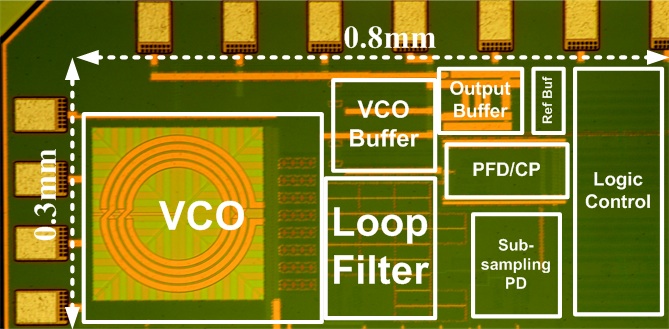

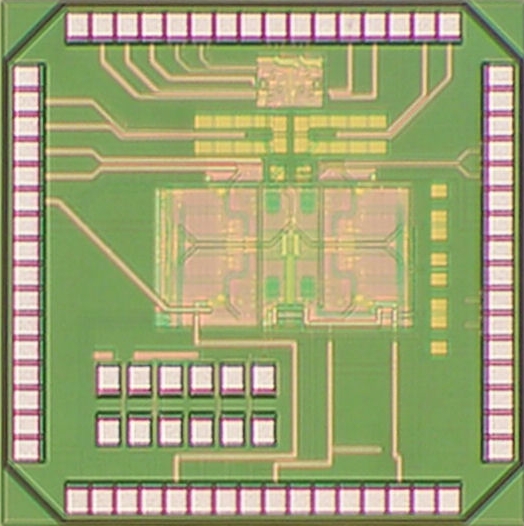

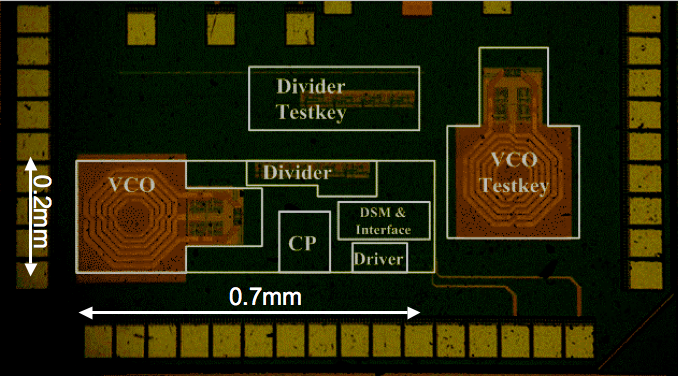

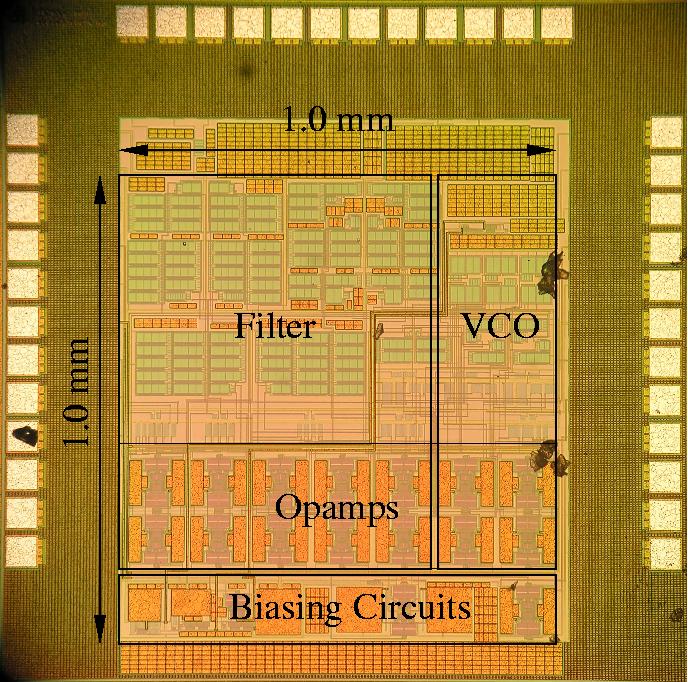

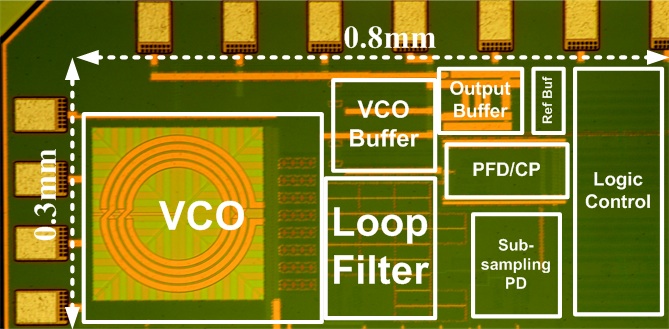

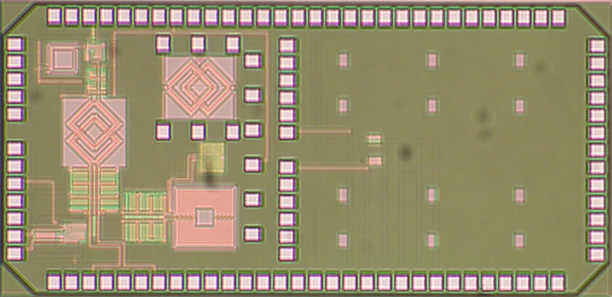

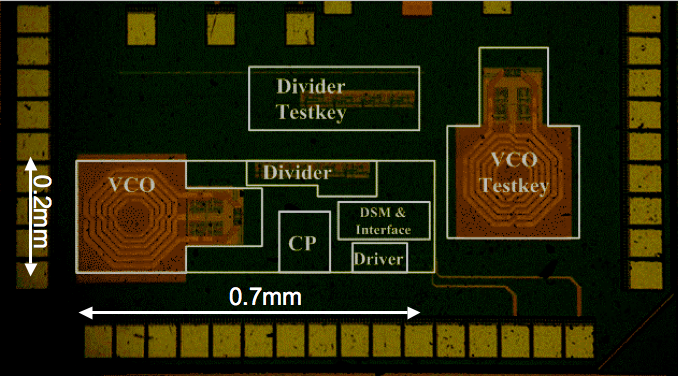

Phase Locked Loop

(65nm CMOS)

[CICC11]

Zero-Crossing Based Pipelined ADC

(65nm CMOS)

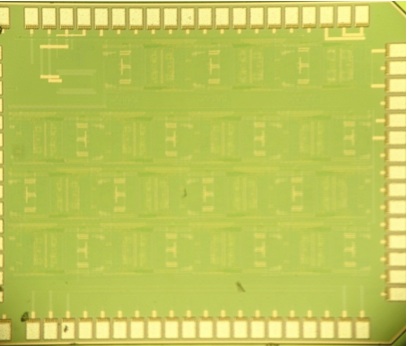

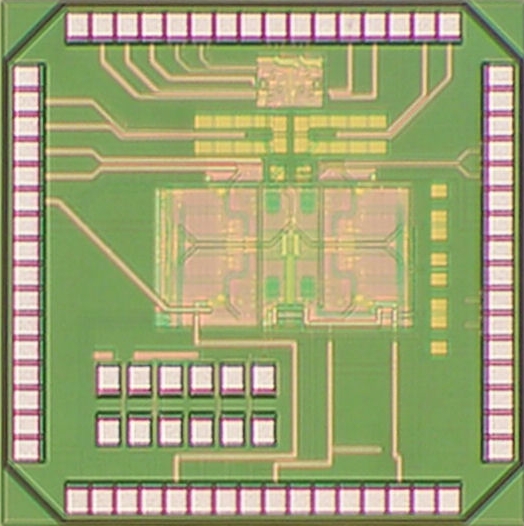

Wake-up Receiver using Ultrasound Data Communications

(65nm CMOS)

[VLSI11, JSSC13]

Current-Charge-Pump Pipelined ADC

(90nm CMOS)

[TCASII11]

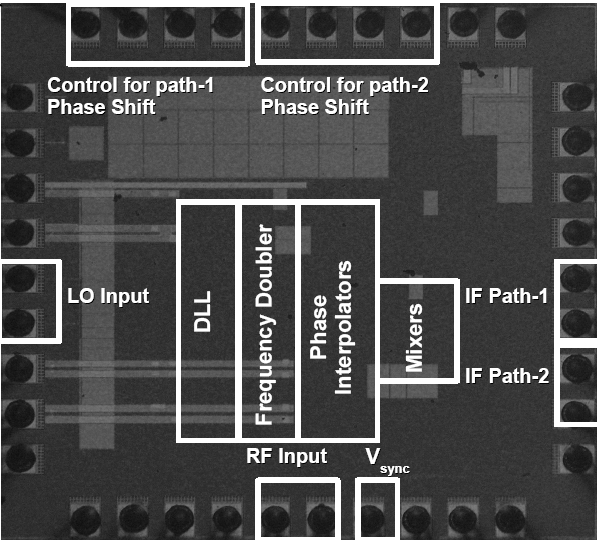

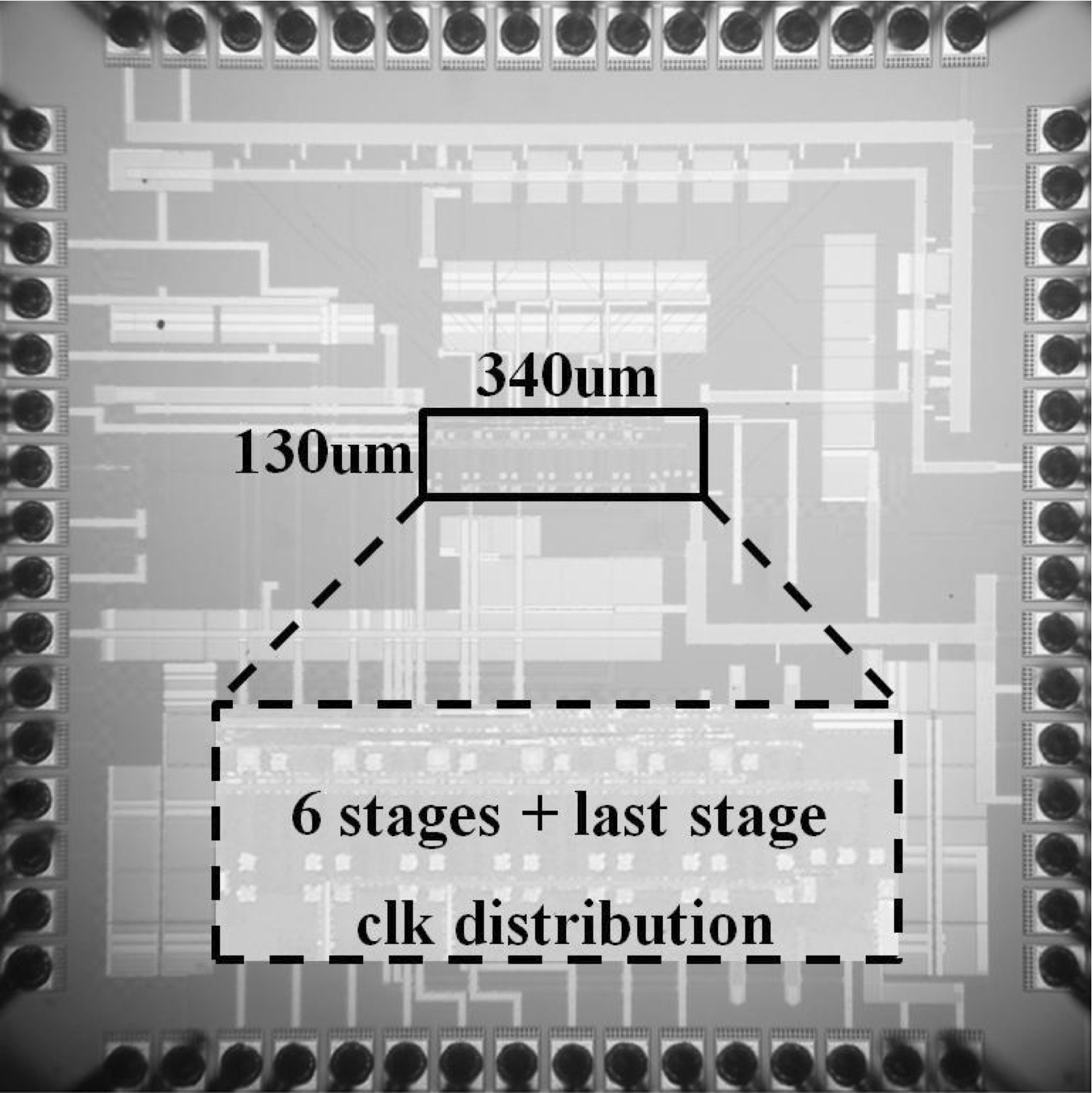

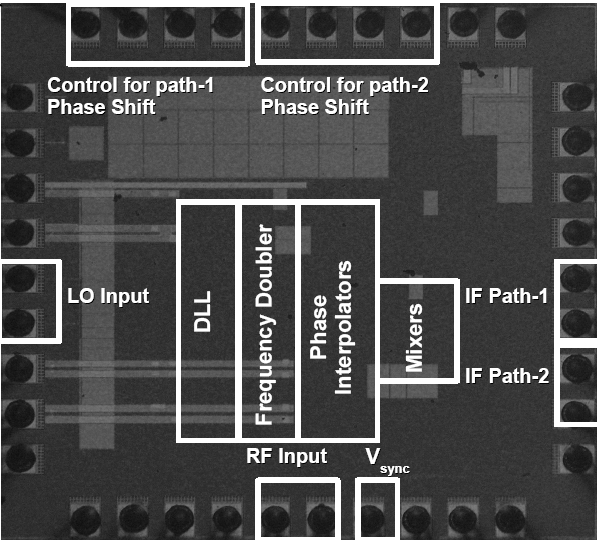

CMOS Phase Shifter with Frequency Doubling for

Multiple-Antenna Transceiver Systems

(90nm CMOS)

[RWW11]

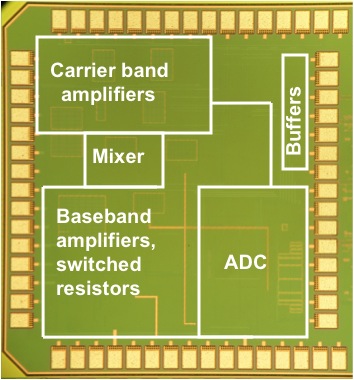

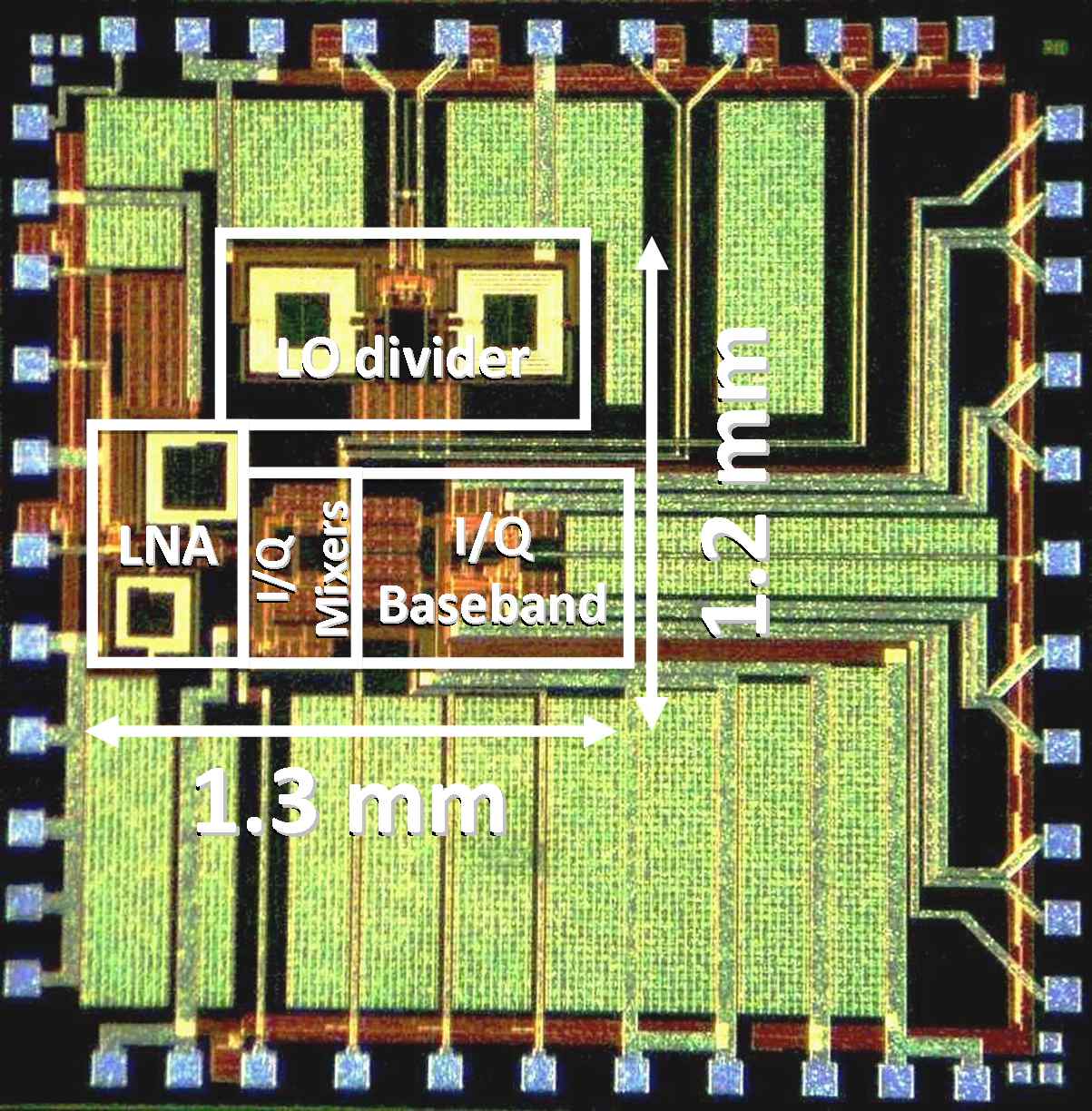

0.6V 900MHz Receiver with Interference Cancellation

(65nm CMOS)

[VLSI10, JSSC11]

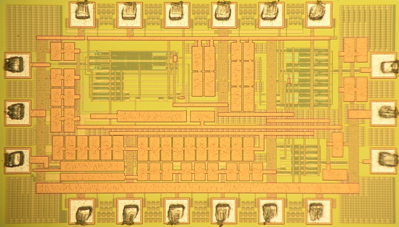

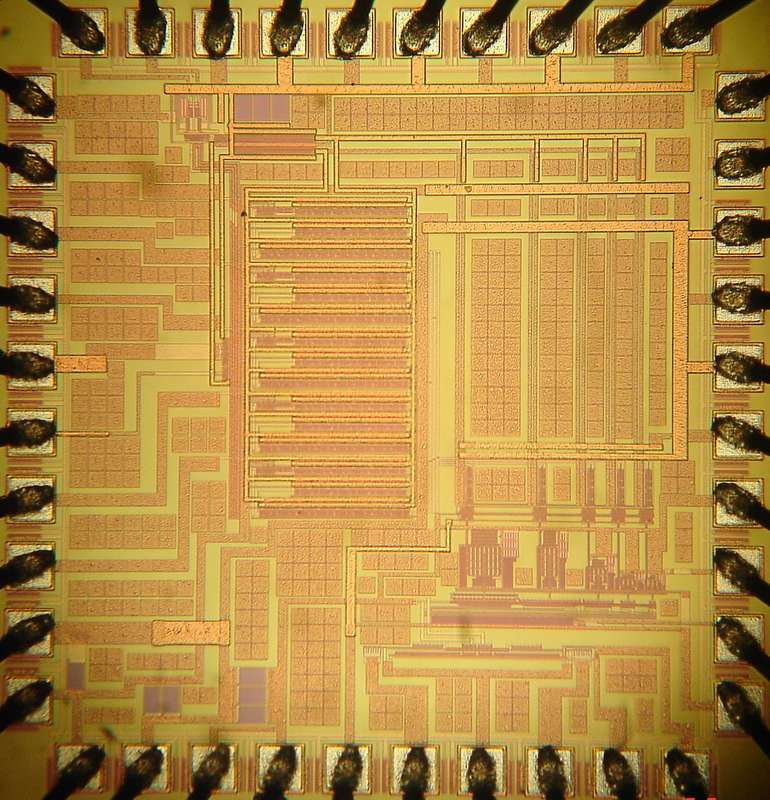

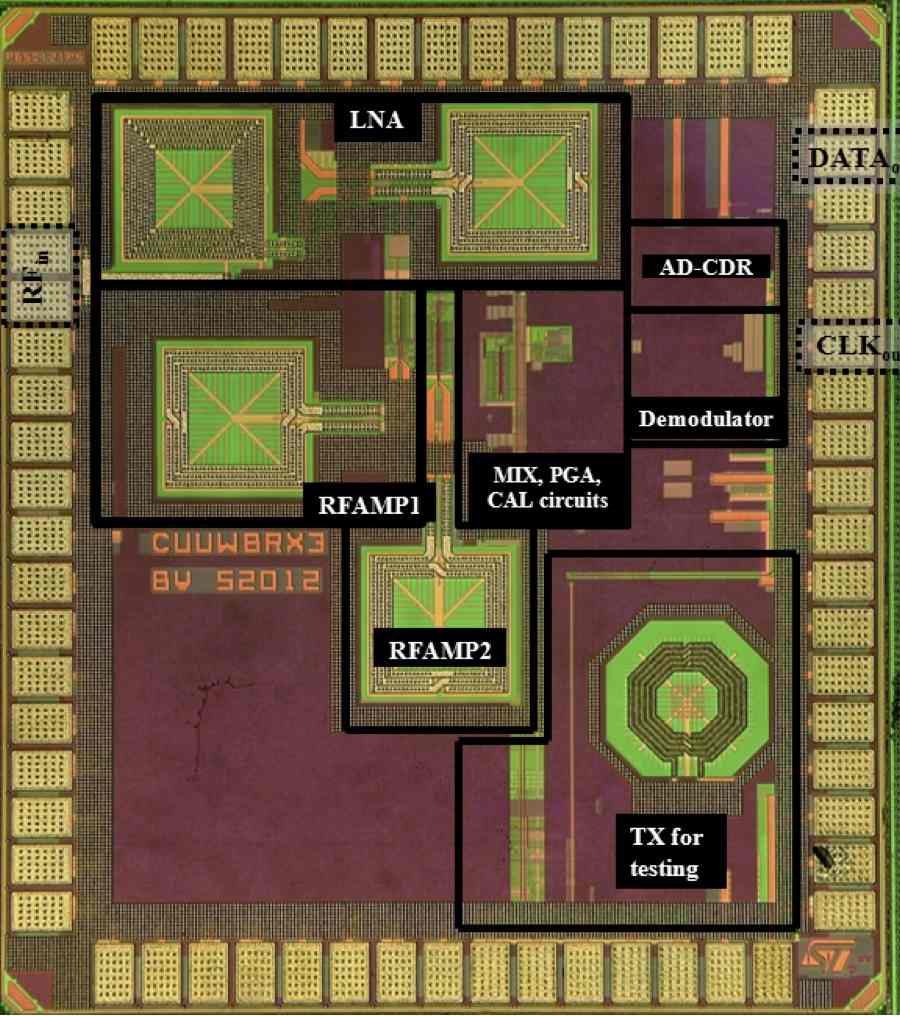

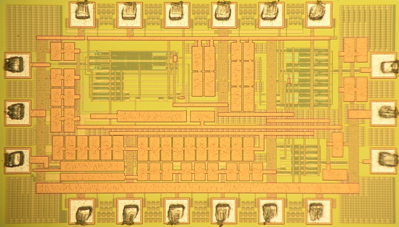

Direct Conversion Front End with Digitally Assisted IIP2 Background Self Calibration

(130nm CMOS)

[ISSCC10, JSSC11]

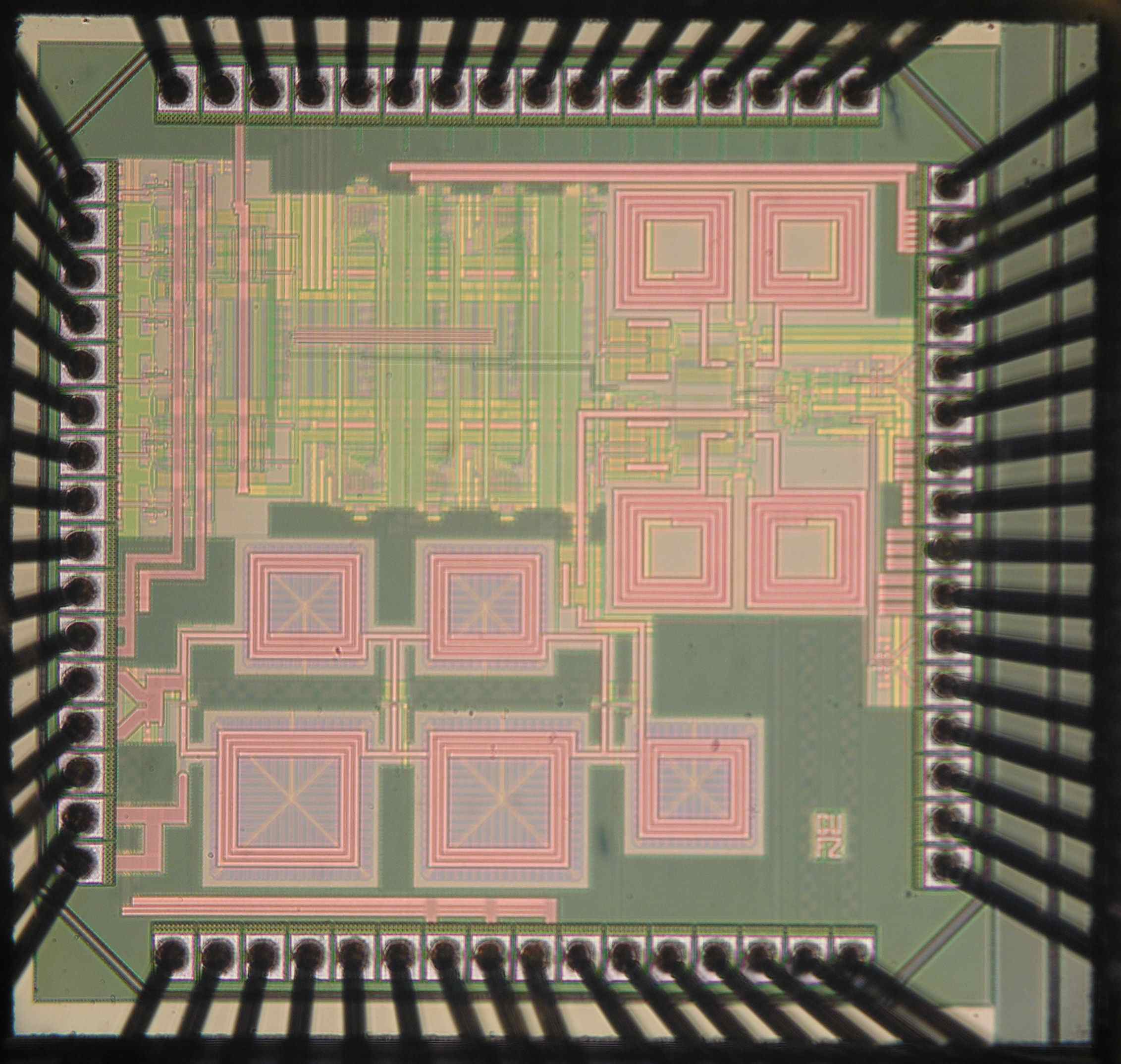

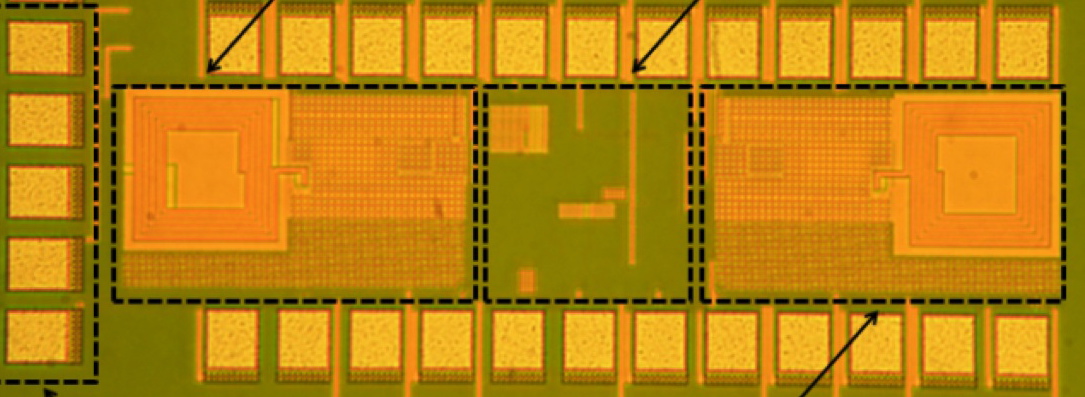

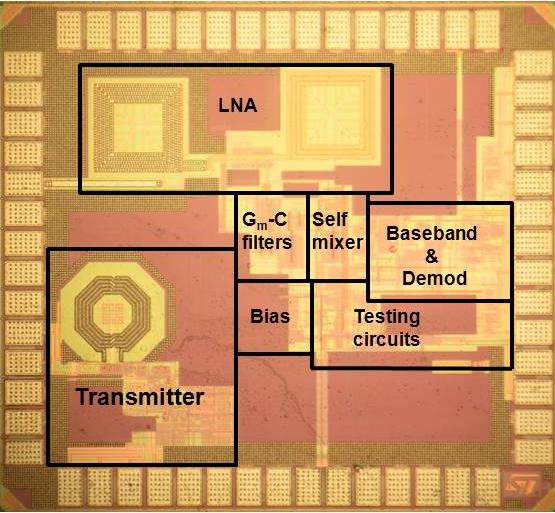

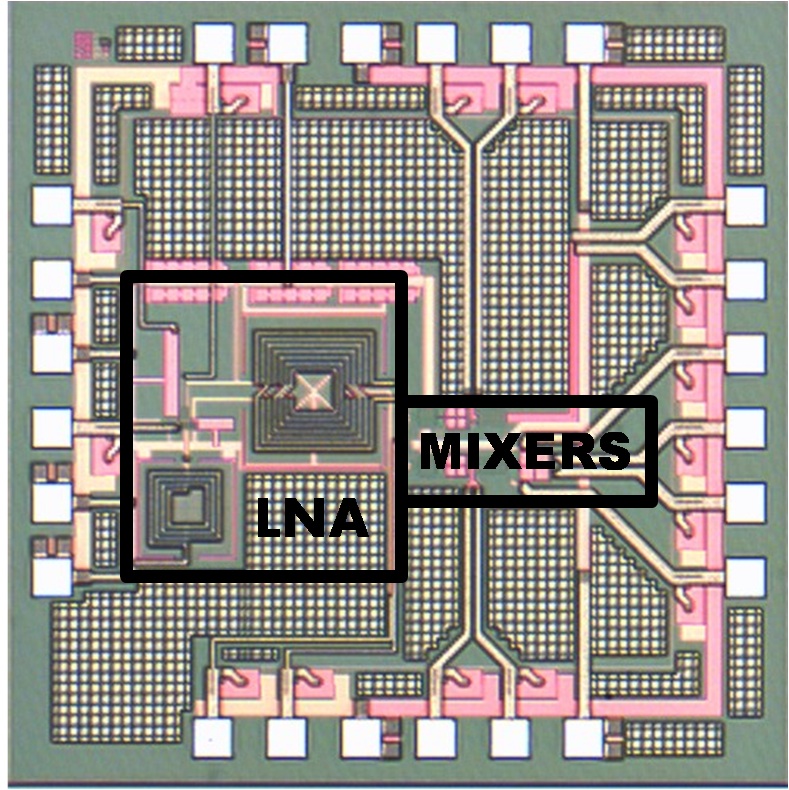

IR-UWB Transceiver Chipset Using Self-Synchronizing OOK Modulation

(90nm CMOS)

[ISSCC10, JSSC11]

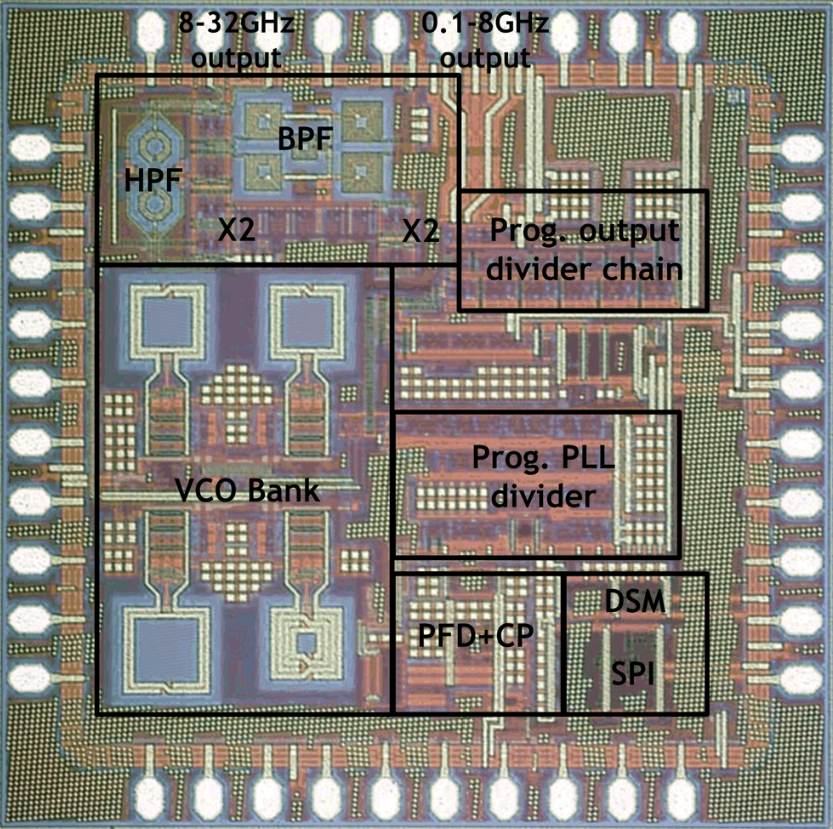

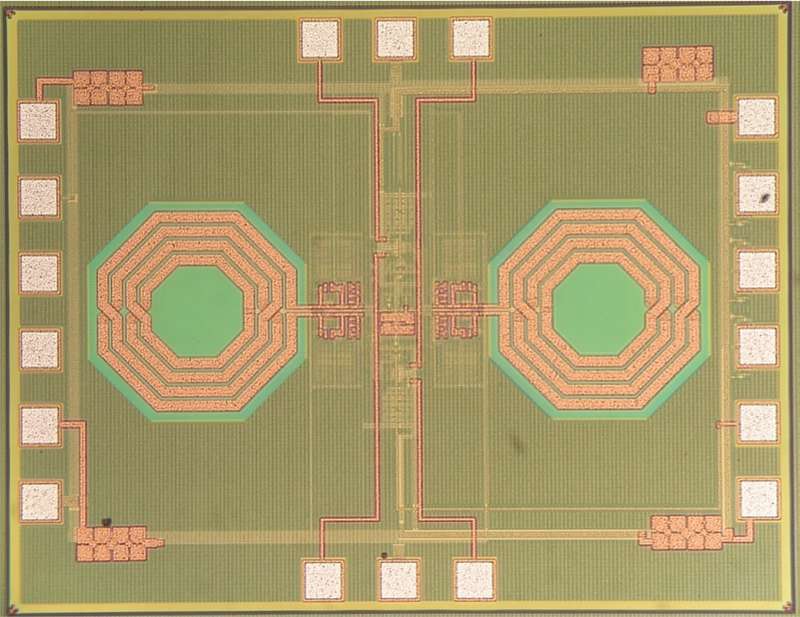

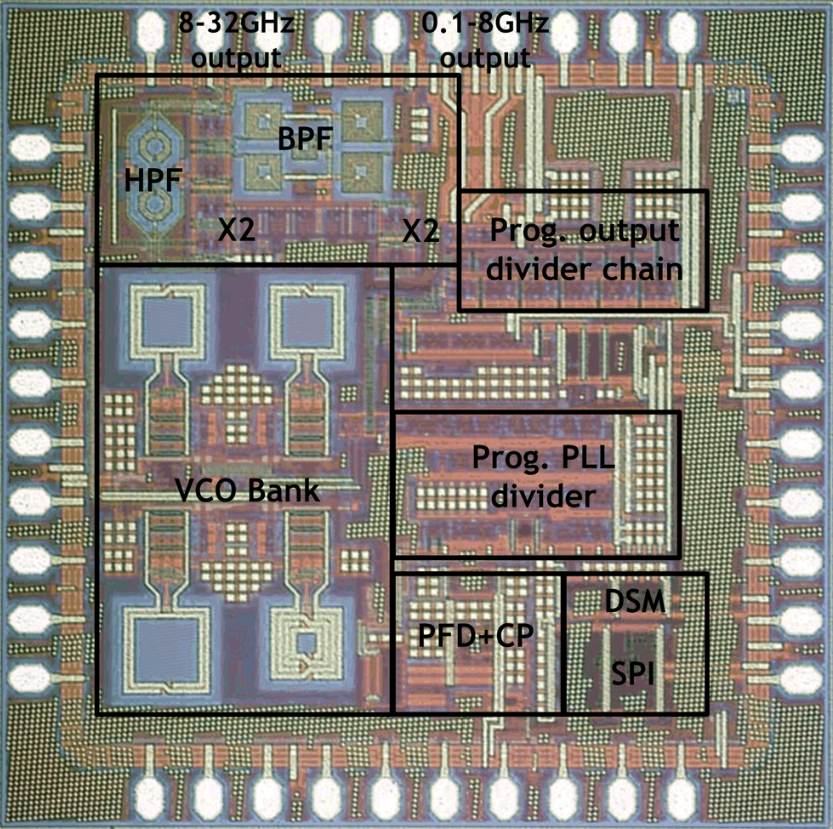

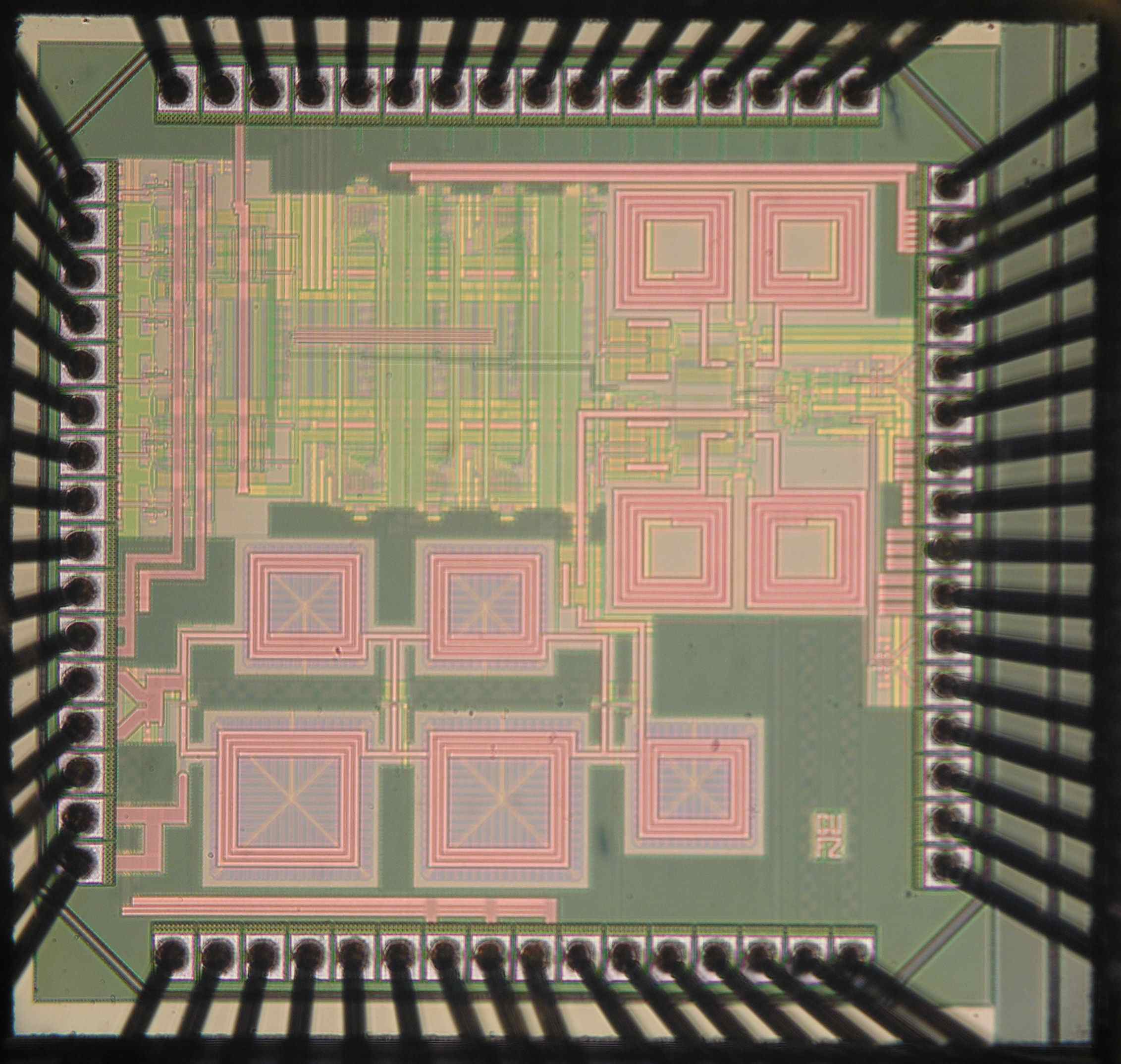

A Single-Chip 0.125-32GHz Signal Source

(180nm SiGe BiCMOS)

[RFIC08] and [JSSC11] (modified version)

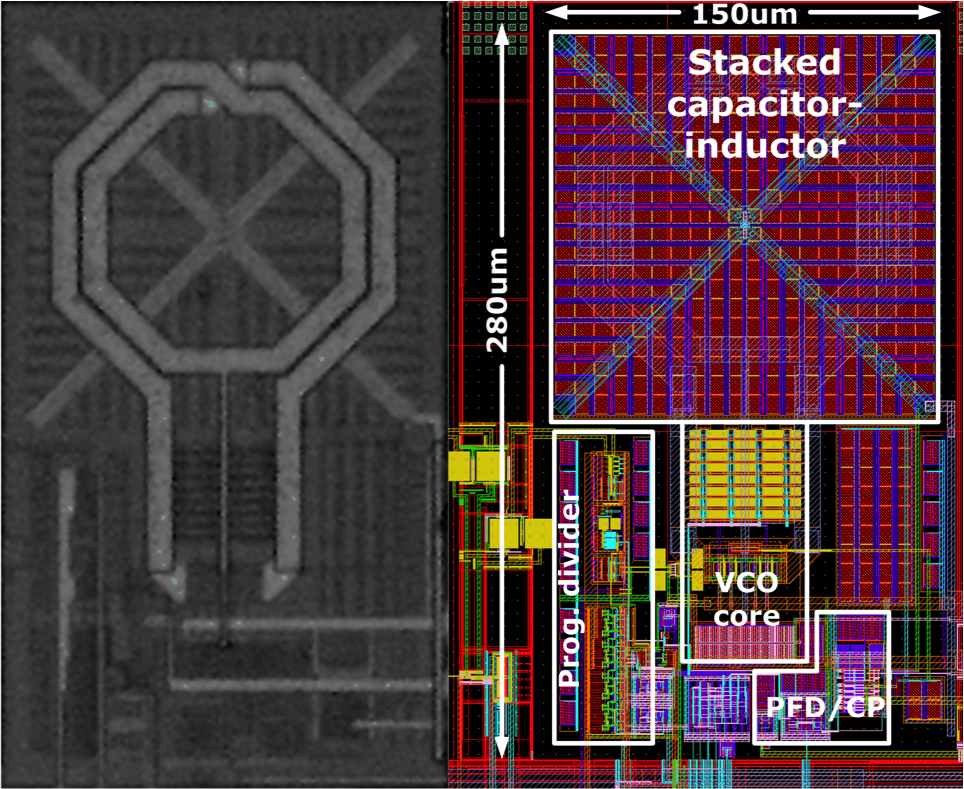

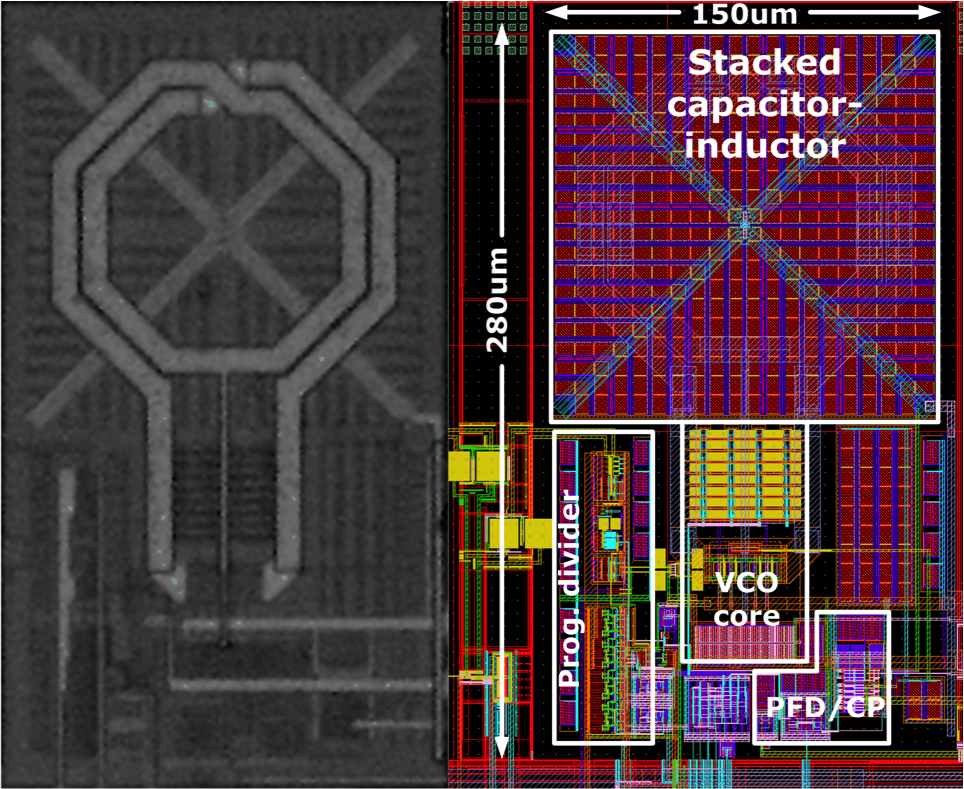

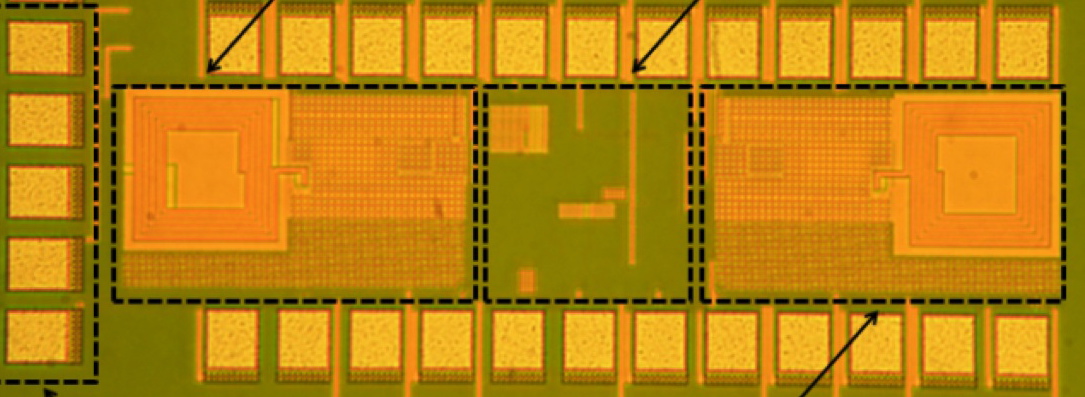

A 0.042-mm2 Fully Integrated Analog PLL with Stacked

Capacitor-Inductor

(45nm CMOS)

[ESSCIRC08]

Voltage Reference for Ultra Low Voltage Supply Operation

(90nm CMOS)

[CICC08]

UWB Pulse Radio Receiver

(90nm CMOS)

[RFIC08, JSSC09]

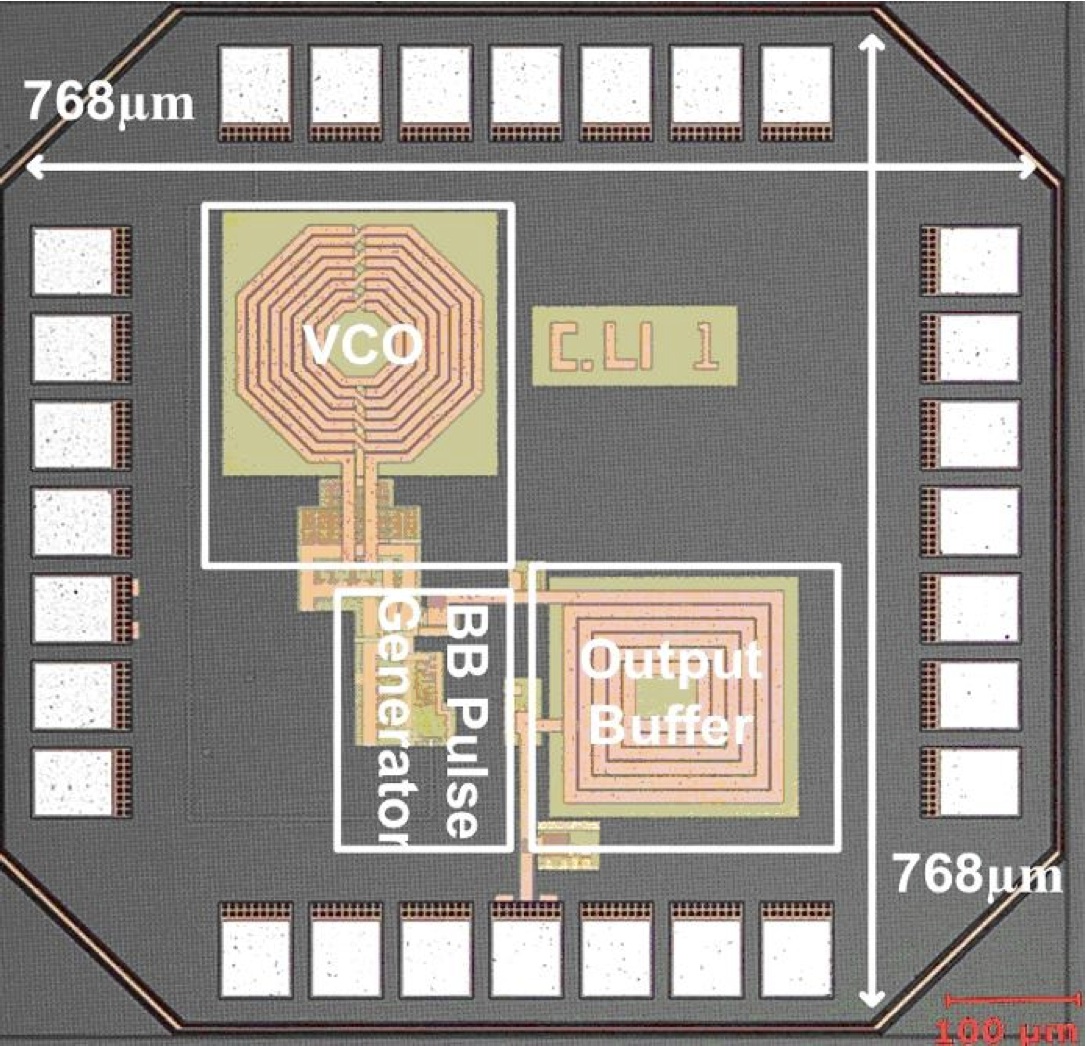

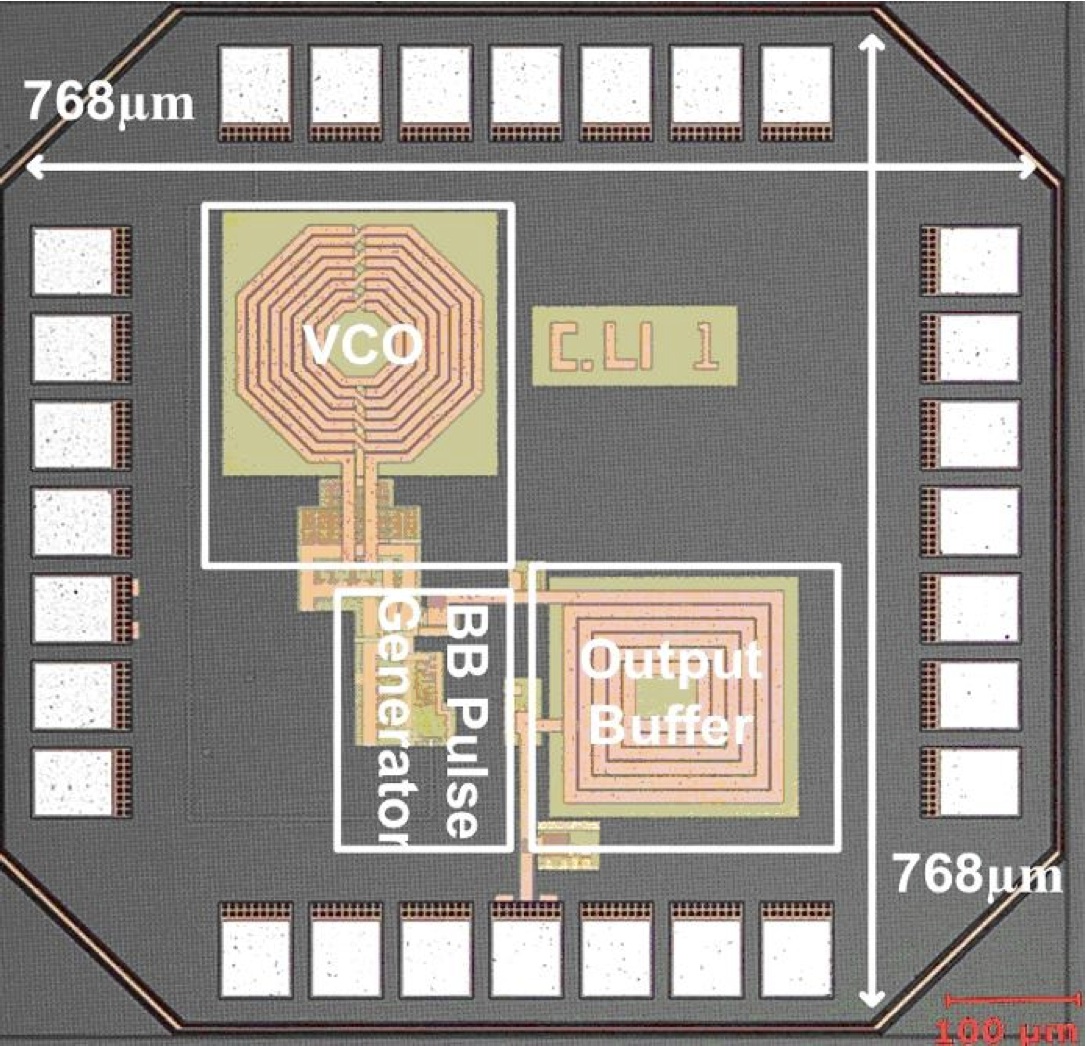

UWB Pulse Radio Transmitter

(90nm CMOS)

[RFIC08, JSSC09]

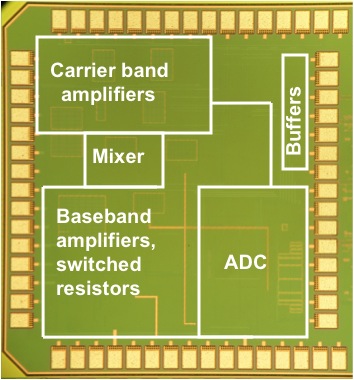

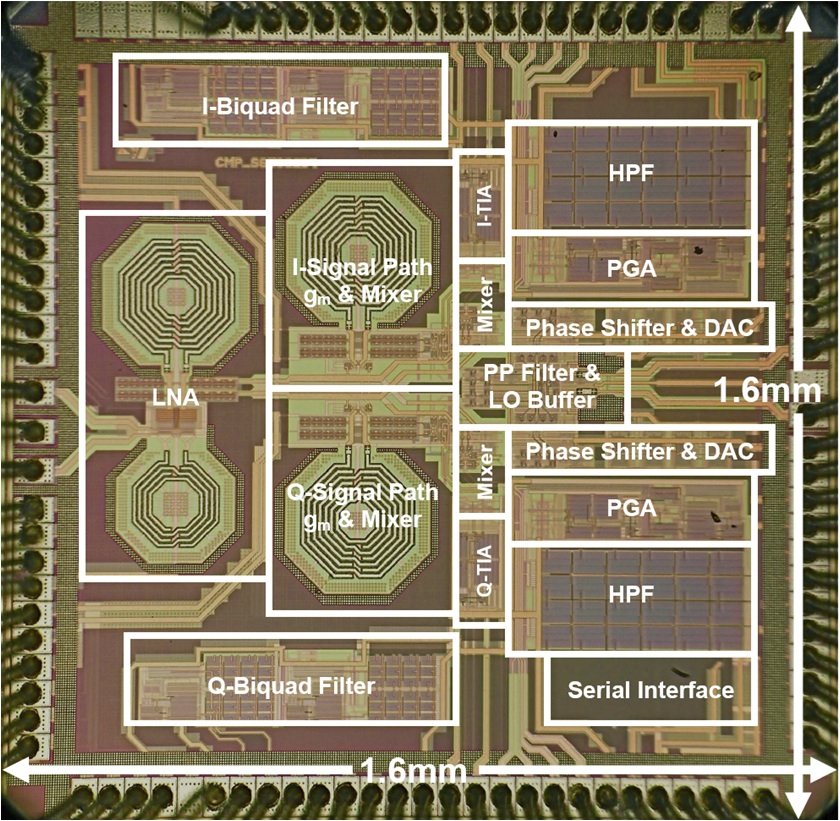

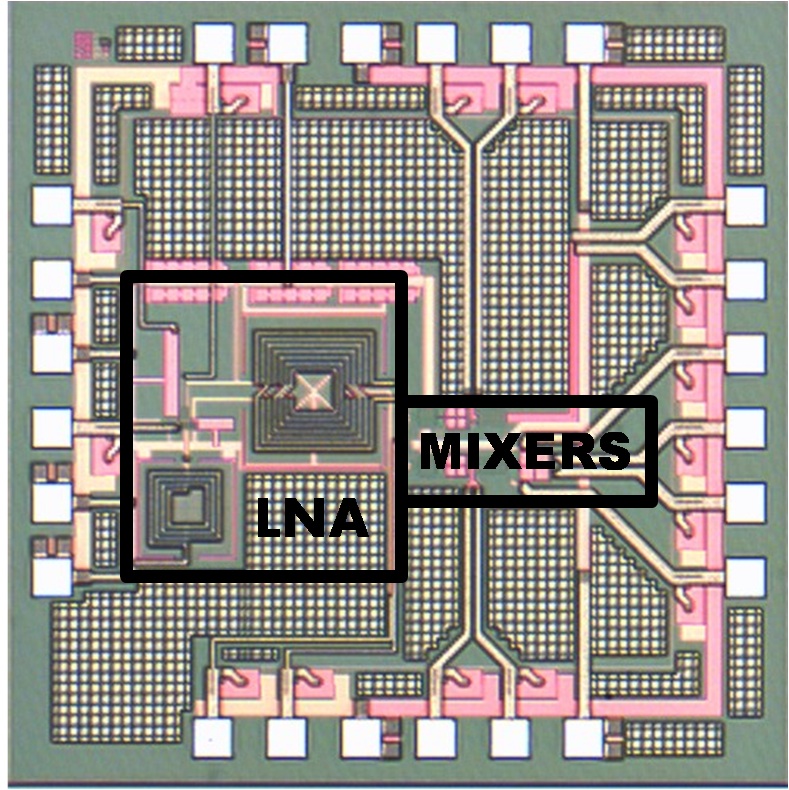

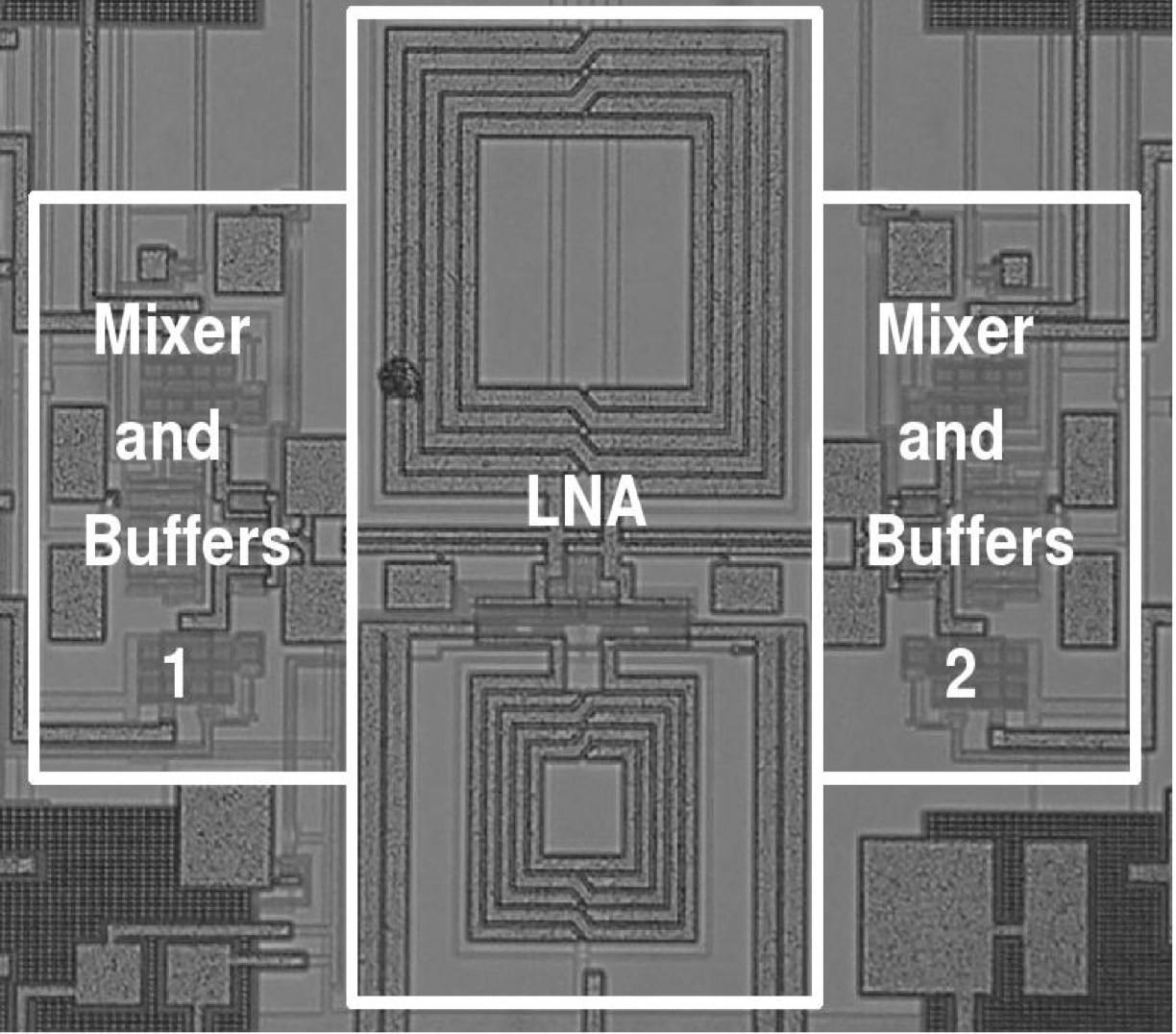

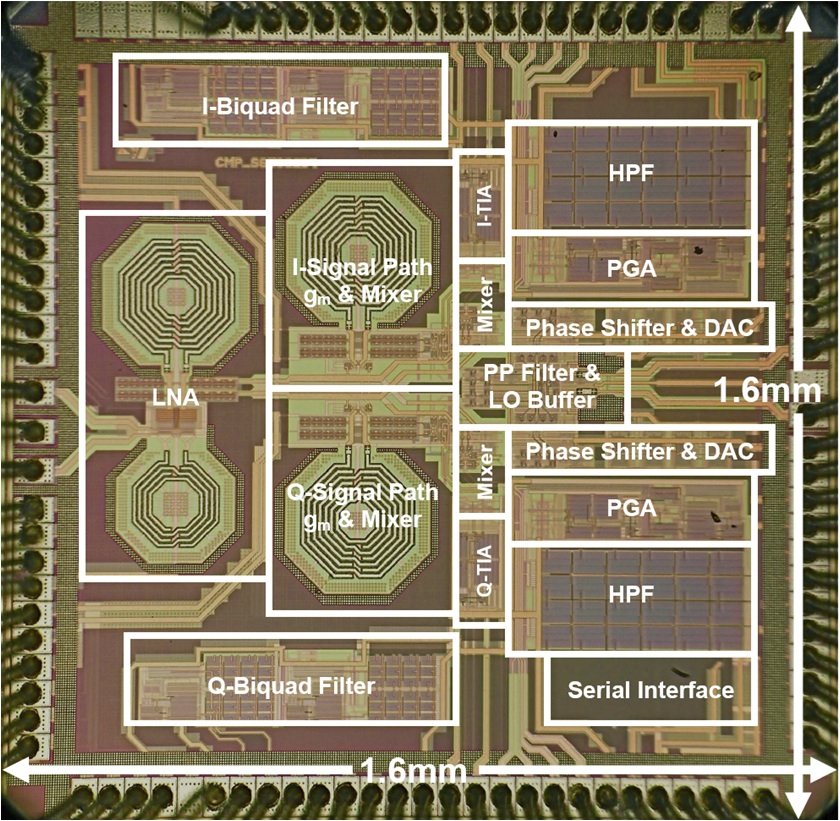

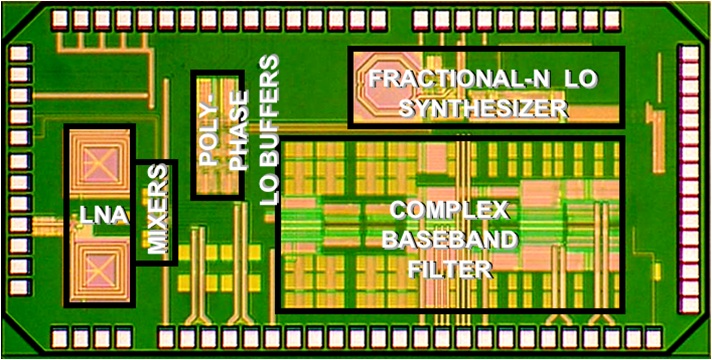

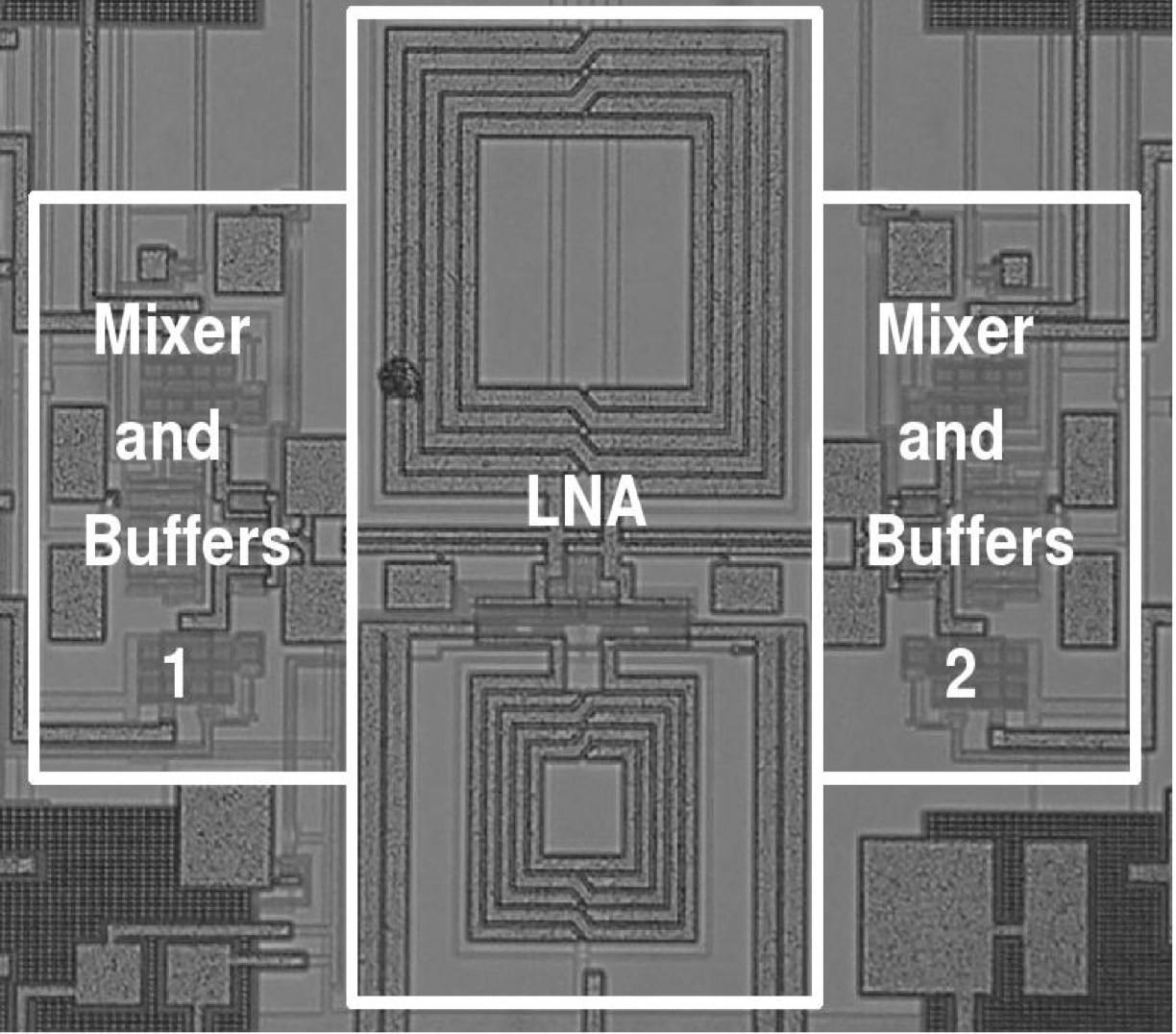

High Performance 2GHz Direct Conversion Front End

(130nm CMOS)

[RFIC08, JSSC09]

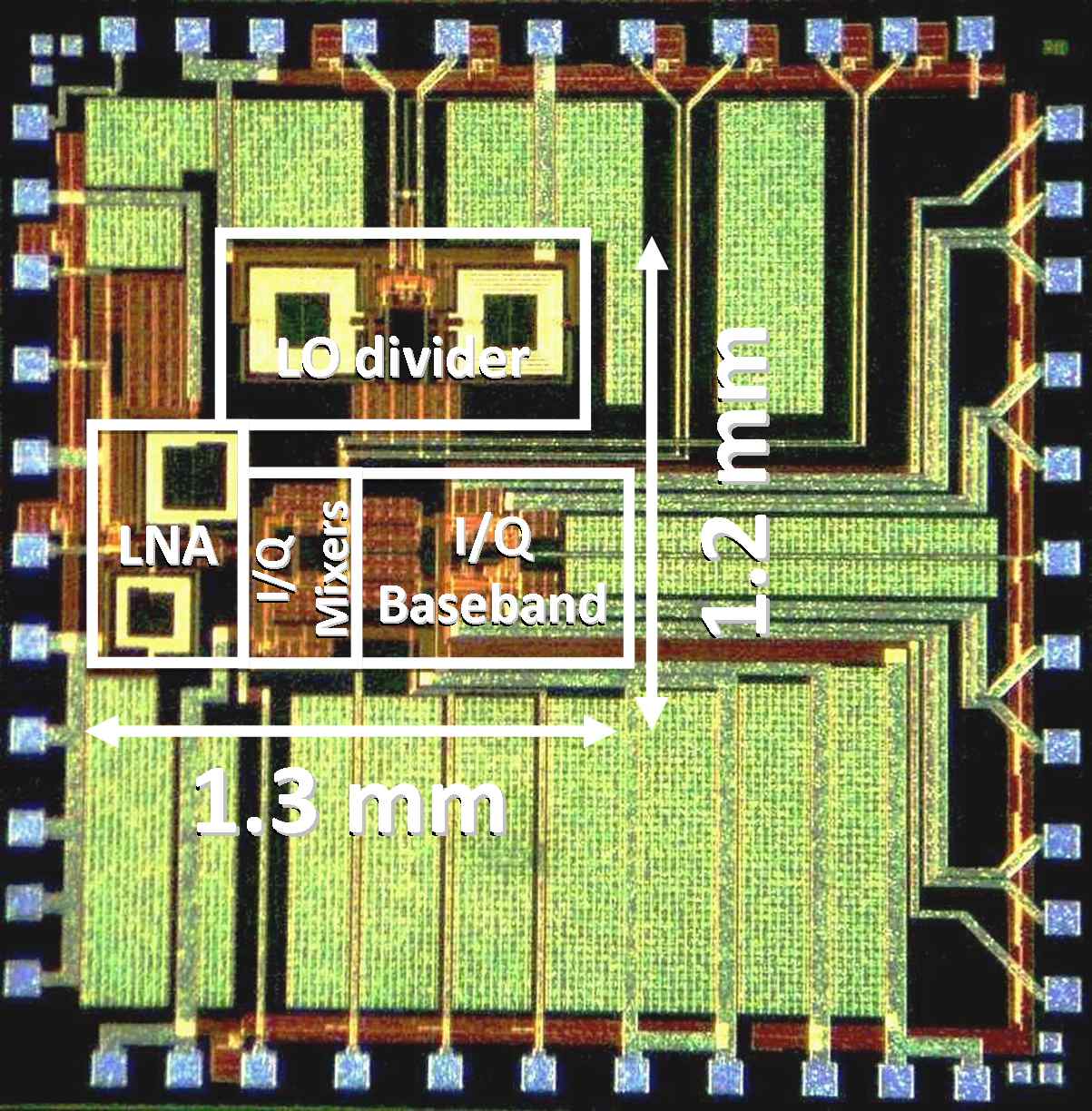

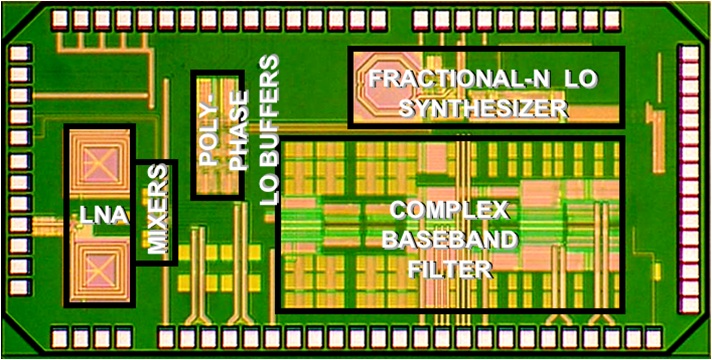

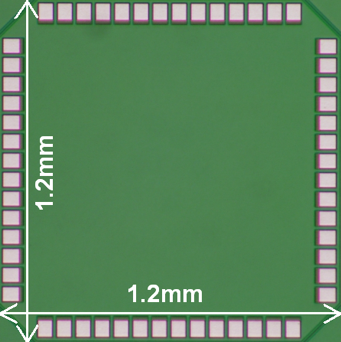

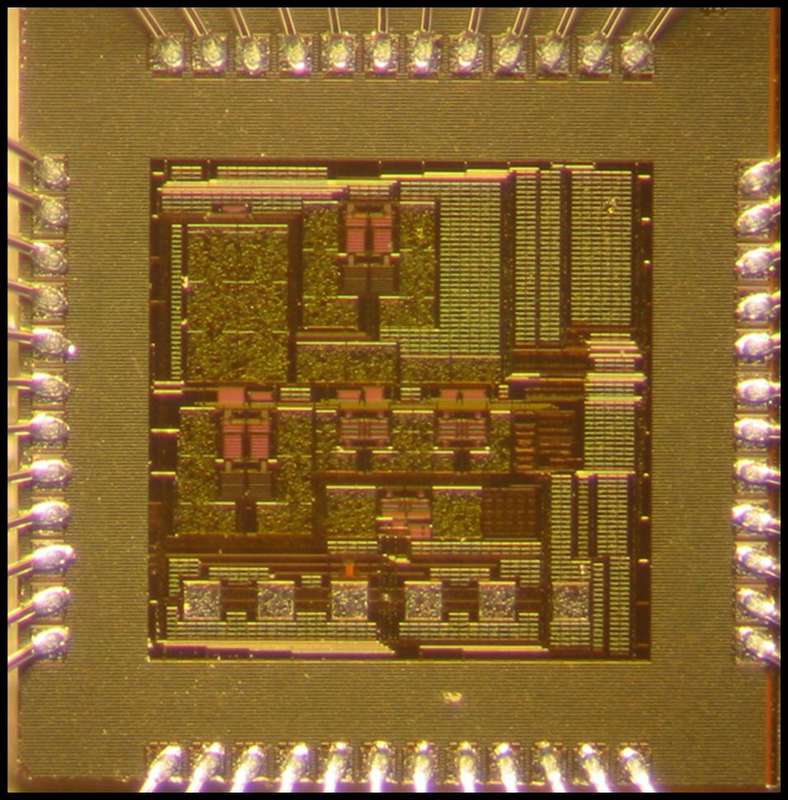

0.6V Highly Integrated 2.4GHz Receiver and Synthesizer

(90nm CMOS)

[ISSCC08, 2010]

2.6GHz Inductive Power Delivery for Contactless Test

(90nm CMOS)

[ICMTS08]

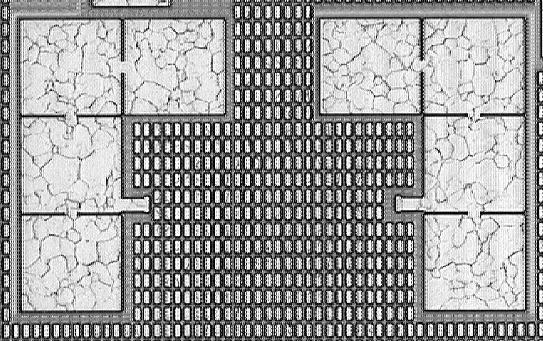

Ring Oscillator Mismatch Test Structure

(0.25 um/40 GHz BiCMOS)

[CICC07]

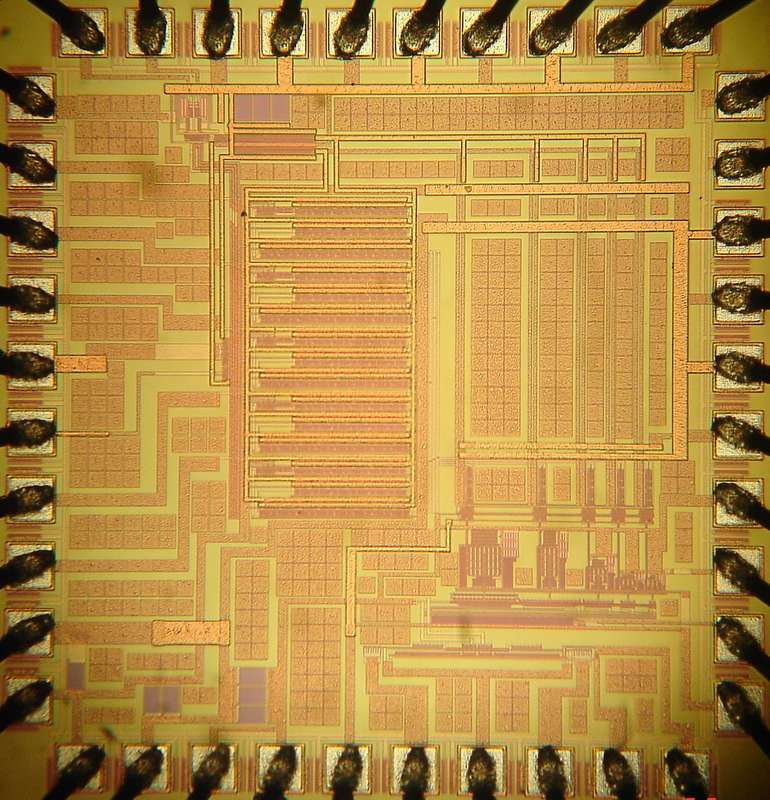

0.5V 8bit 10Msps pipelined ADC

(90nm CMOS)

[VLSI07, JSSC08]

0.5V 2.4GHz Sliding-IF Receiver

(90nm CMOS)

[RFIC07, JSSC08]

0.65/0.5V Frequency Synthesizer

(90nm CMOS)

[ISSCC07]

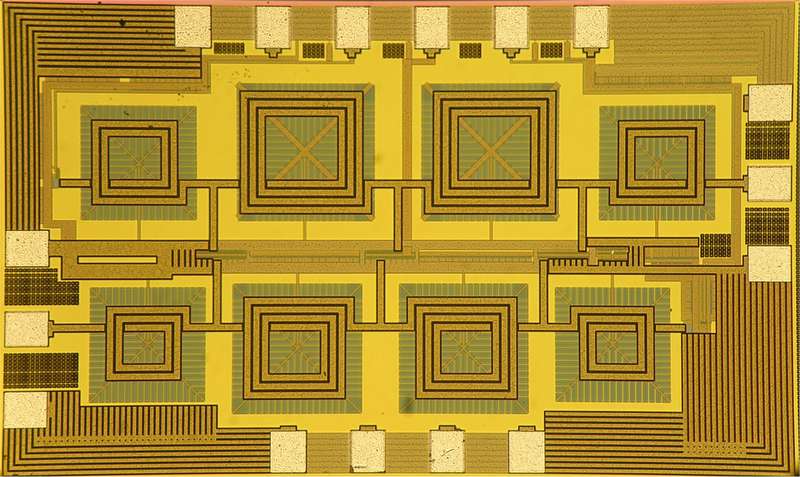

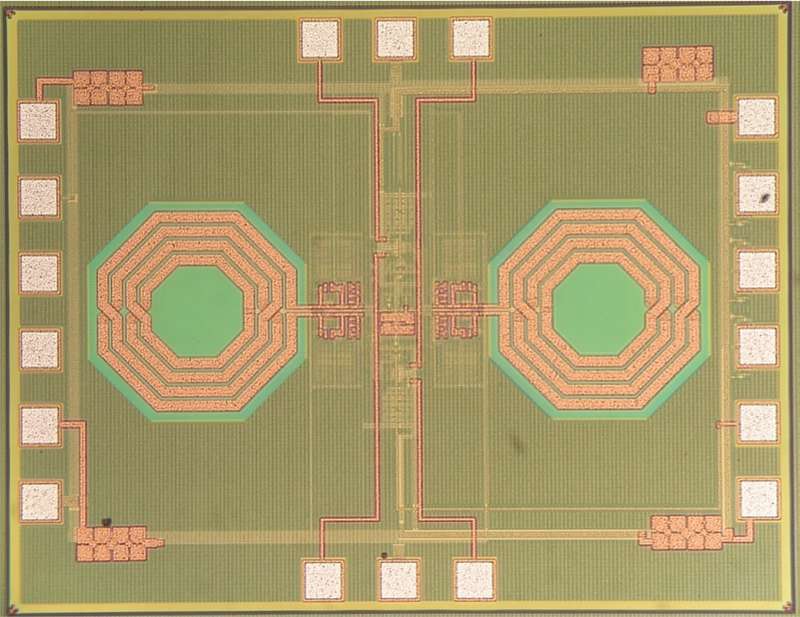

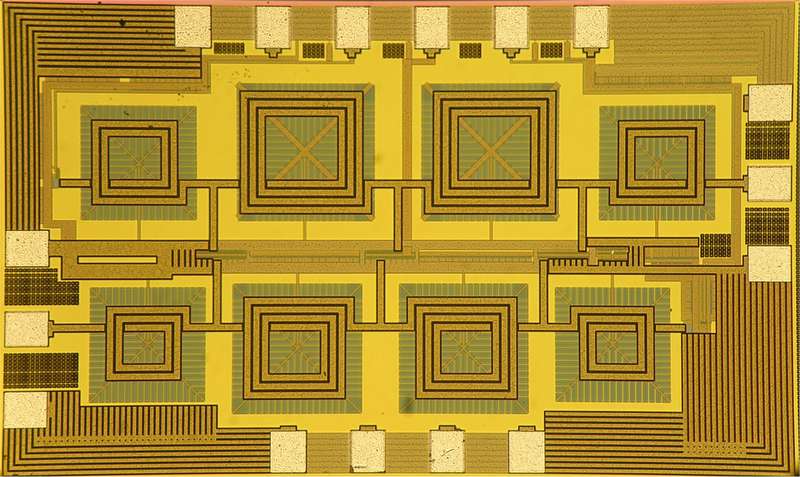

Quadrature VCO with Capacitive Common-Source

coupling

(0.25 um/40 GHz BiCMOS)

[ESSCIRC06]

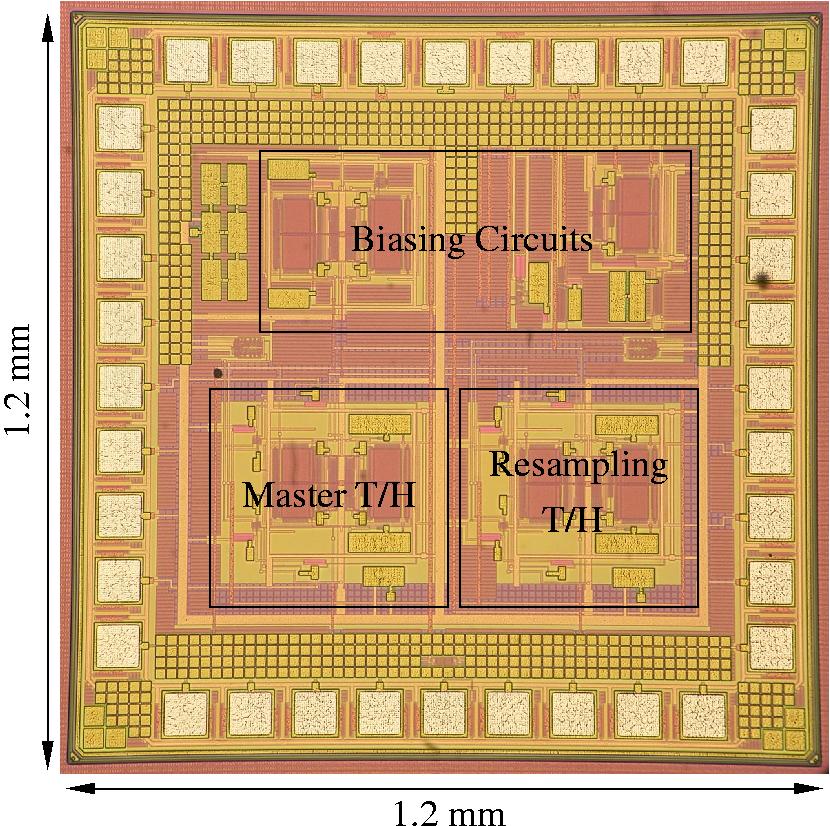

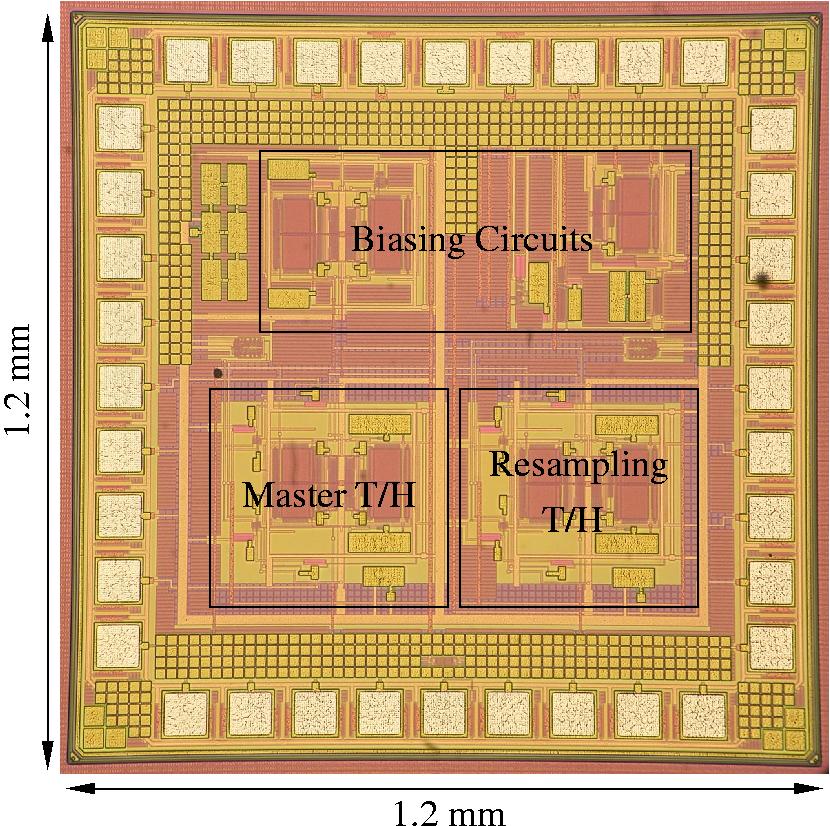

0.5 V Track and Hold Amplifier

(0.25um

CMOS)

[VLSI06, JSSC07]

0.5 V 900MHz RF Front-end

(0.18um

CMOS)

[VLSI06]

5-bit DAC for UWB Pulse Generation

(0.25 um/40 GHz ft BiCMOS)

[ISCAS06]

0.5 V Sigma Delta Converter

(0.18um CMOS)

[ISSCC06, JSSC07]

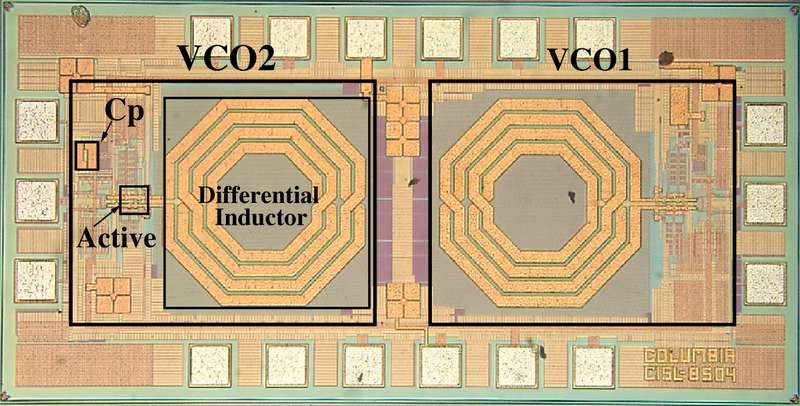

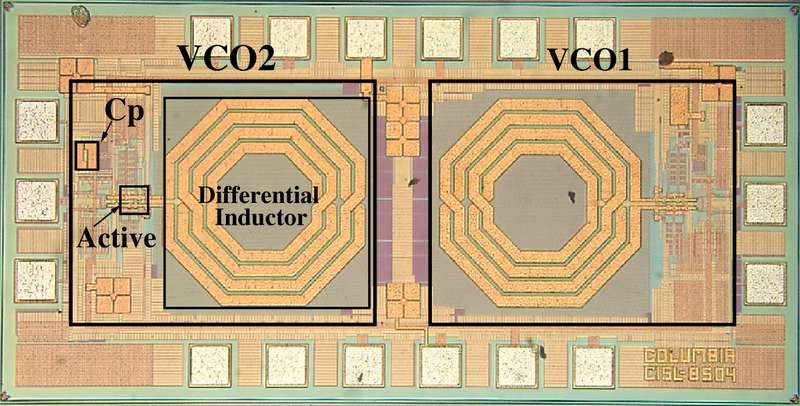

VCO without (VCO1) and with (VCO2) Tail Current Shaping

(0.25 um/40 GHz BiCMOS)

[CICC05, JSSC06]

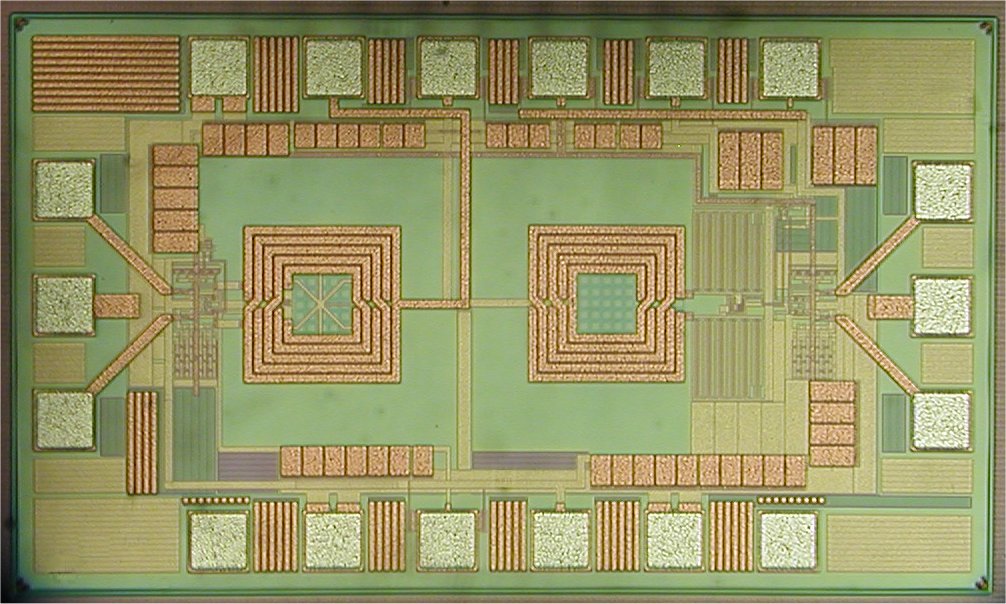

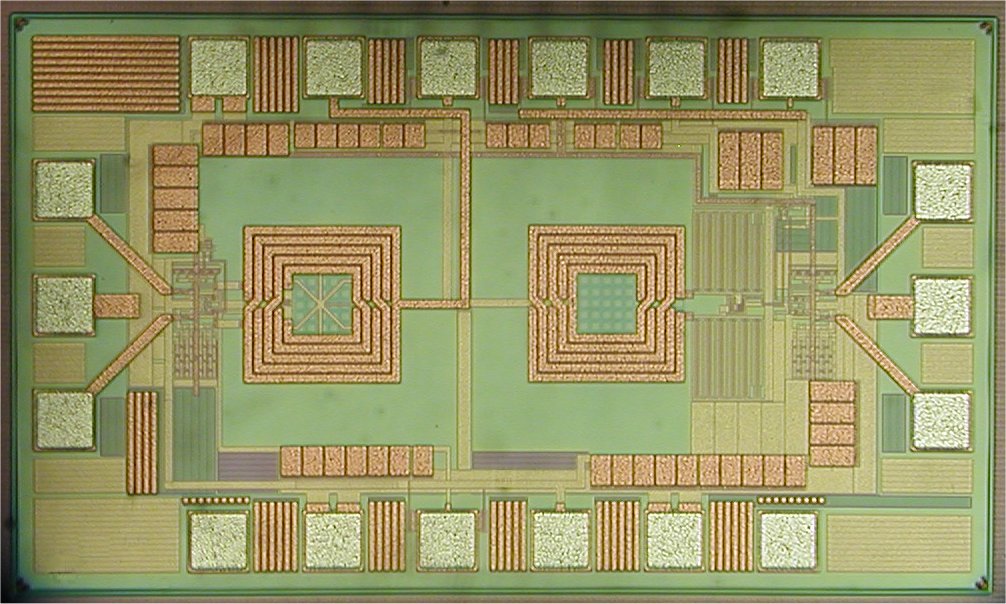

VCO in a coil

(0.25 um/40 GHz BiCMOS)

[CICC05, JSSC06]

Distributed CMOS LNA for UWB applications

(0.18um CMOS)

[VLSI05, JSSC06]

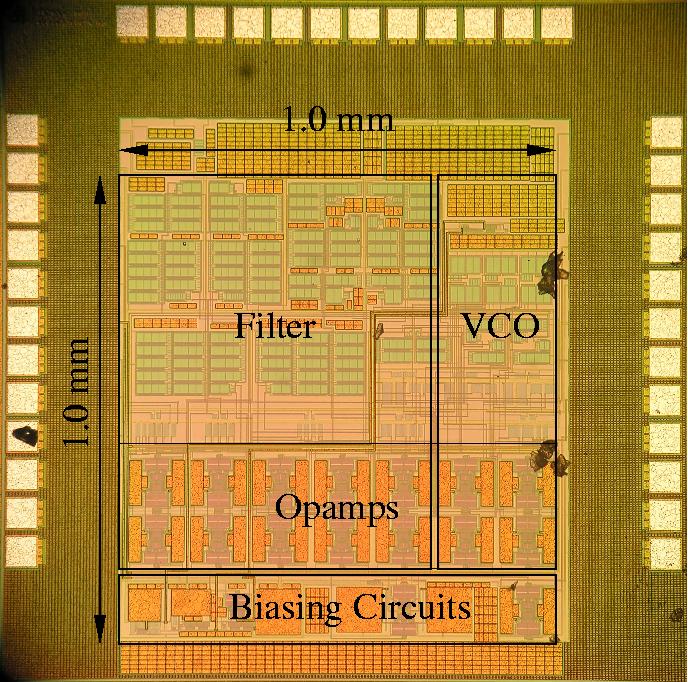

0.5 V Filter With PLL-Based tuning

(0.18um CMOS)

[ISSCC05, JSSC05]

0.5 V Bulk-input amplifier

(0.18um CMOS)

[ESSCIRC04, JSSC05]