|

[a]

[b]

[b]

|

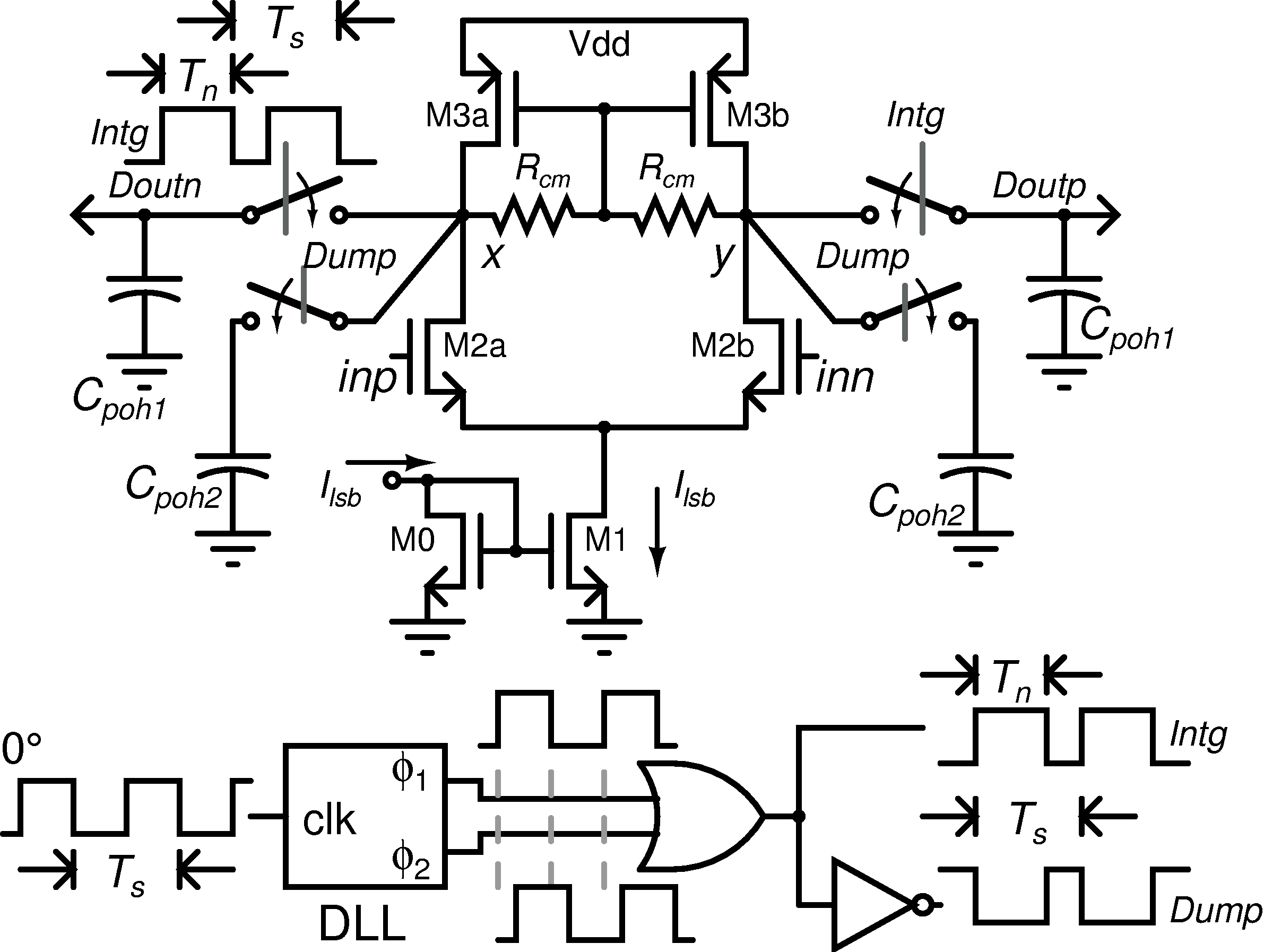

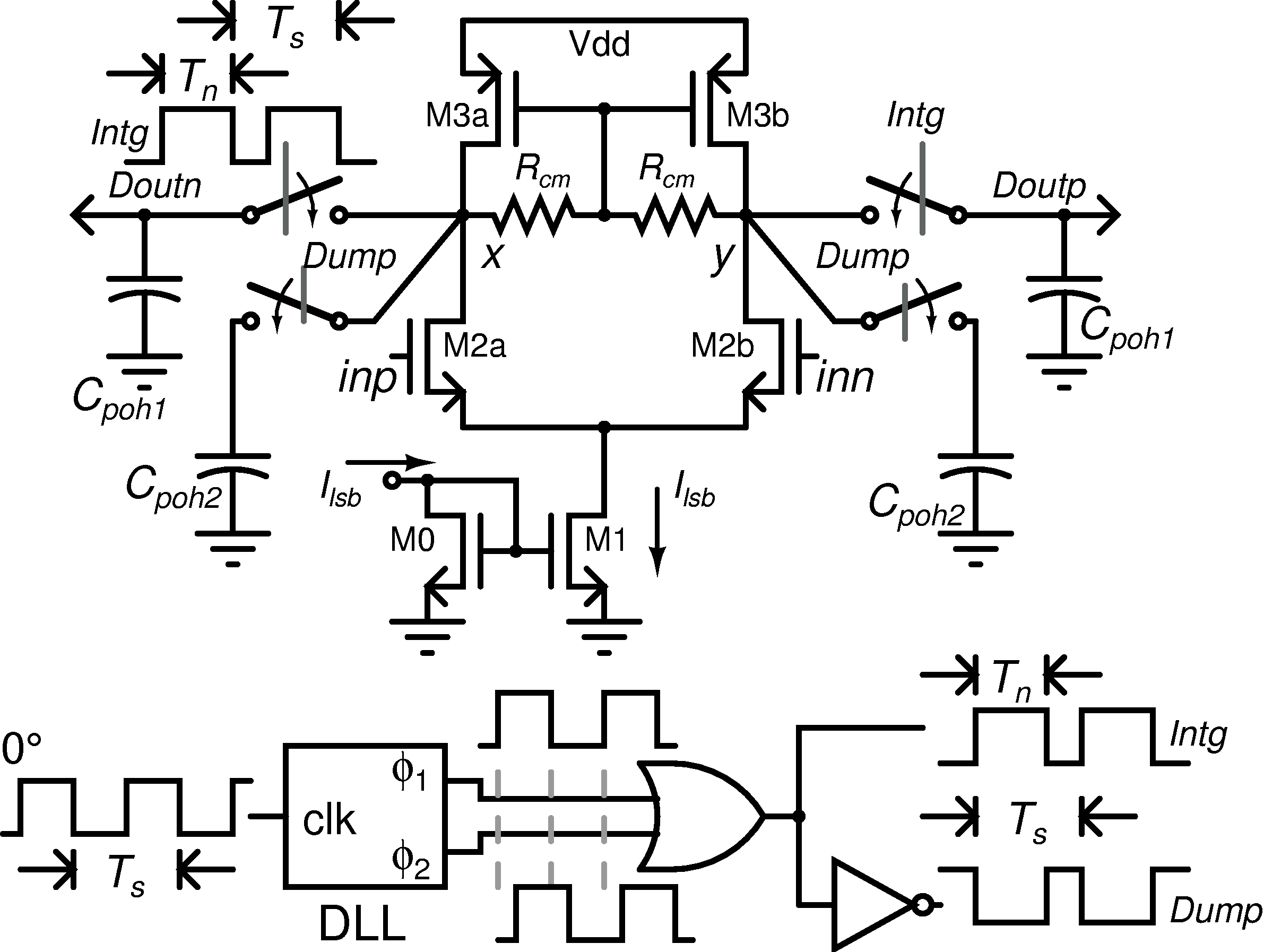

A ZOH-DAC plus WIBF system can be implemented by modifying a First-order Hold DAC by adding a switch in between the current-output ZOH-DAC and the integrating capacitor Cpoh [3]. When the switch is ON for a duration Tn < Ts, charge proportional to the difference between two consecutive samples is accumulated on Cpoh. When it turns OFF, Cpoh holds that charge for the rest of the sample period. A circuit implementation is shown in Fig. 4(a) where the current is steered between capacitors depending on the digital input [6].

|

[a]

[b]

[b]

|

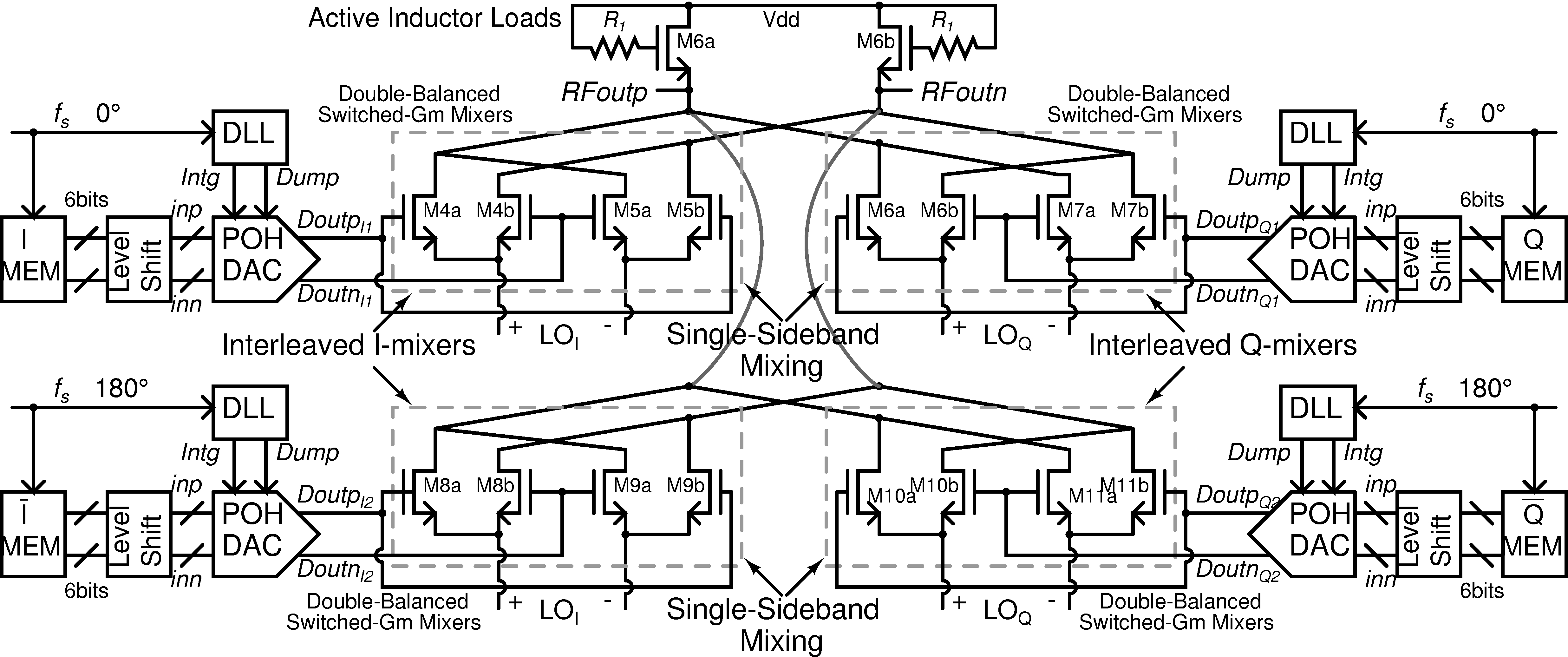

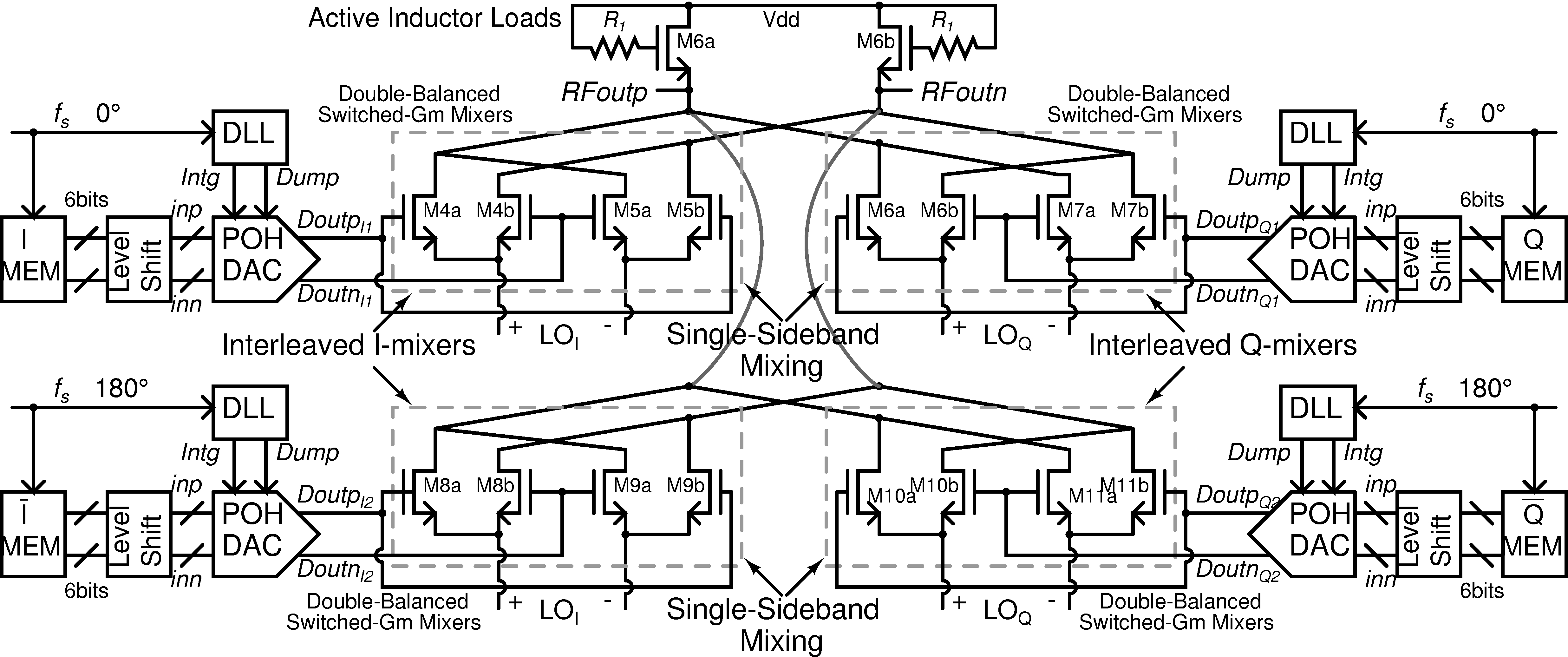

The base-band signals from the POH-DACs were interleaved and up converted in the single-sideband mixing stage. A switched-transconductor based mixer was used; pseudo-balanced 4 GHz LO signals with rail-to-rail swing were applied at the source of the transconductors (M4-M11 in Fig. 4(b)). The POH-DAC outputs were DC-coupled to the mixers. Transistors (M6a-b) with resistances R1 at the gates were used to provide bandwidth extension by inductive load peaking. Interleaving was simultaneously achieved at the load by summing the up converted transconductor currents proportional to the outputs of the POH-DACs working at 0/180 degree phases of the sampling clocks. With the addition of the quadrature LO and quadrature signal paths, the mixer also performed single-sideband up conversion.